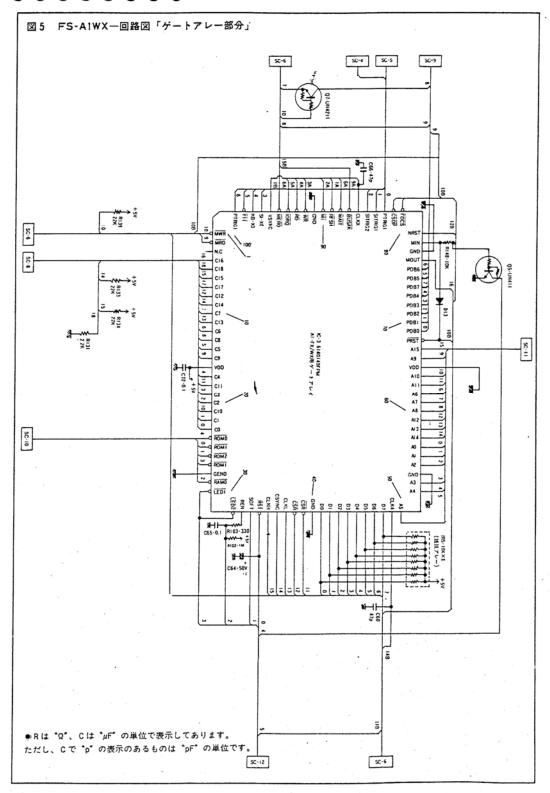

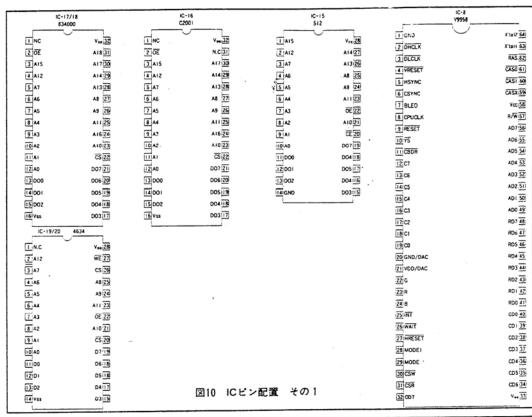

## IC/Oゲートアレイ ●カスタム6140140FPM端子機能

| ごンNo | 信号名   | 1/0            |                                                 |      |          |      |                    |

|------|-------|----------------|-------------------------------------------------|------|----------|------|--------------------|

| 1    | MWR   | 1/0            | O:SRAM/FDC/MAIN RAMのWR信号 I:RESET時H-/ーマル/L-高速モード |      |          |      |                    |

| 2    | MRD   | 0              | SRAM/FDC/MAIN-RAMのRD記号                          |      |          |      |                    |

| 3    |       |                | 未使用                                             |      |          |      |                    |

| 4    | C16   | 0              | ROMP FUZICA                                     |      |          |      |                    |

| 5    | C18   | 1/0            | O:ROMアドレスバス I:RESET時H-DOS2有/L-無                 |      |          |      |                    |

| 6    | C15   | 1/0            | O:ROMアドレスバス<br>I:RESET時H-ノーマルモード/L-高速モ          | ード禁止 | Ł        |      |                    |

| 7    | C17   | 0              | ROMPドレスバス                                       |      |          |      |                    |

| 8    | CI2   | 0              | ROM/SRAMアドレスバス                                  |      |          |      |                    |

| 9    | C14   | 1/0            | O:ROMアドレスバス I:RESET時H-WX/L-FX                   |      |          |      |                    |

| 10   | C7    | 0              | ROM/SRAMアドレスパス                                  |      |          |      |                    |

| П    | C13   | 0              | ROMアドレスパス                                       |      |          |      |                    |

| 12   | C6    | 0              | ROM/SRAMアドレスパス                                  |      |          | 1.75 | T 100 7 100 415    |

| 13   | C8    | 0              | ROM/SRAMアドレスバス                                  | _    | 信号名      | 1/0  | 端子機能               |

| 14   | C5    | 0              | ROM/SRAMアドレスパス                                  | 57   | A14      | -!-  | CPUアドレスパス          |

| 15   | C9    | 0              | ROM/SRAMアドレスバス                                  | 58   | A13      | 1    | CPUアドレスバス          |

| 16   | Vcc   |                | +5V                                             | 59   | A12      | 1    | CPUアドレスバス          |

| 17   | C4    | 0              | ROM/SRAMアドレスパス                                  | 60   | A8       | 1    | CPUアドレスバス          |

| 18   | CII   | 0              | ROM/SRAMアドレスパス                                  | 61   | A7       | 1.   | CPUアドレスバス          |

| 19   | C3    | 0              | ROM/SRAMアドレスパス                                  | 62   | A6       | 1    | CPUアドレスパス          |

| 20   | C2    | 0              | ROM/SRAM/FDCアドレスパス                              | 63   | All      | !    | CPUアドレスパス          |

| 21   | C10   | 0              | ROM/SRAMアドレスバス                                  | 64   | AIO      | 1    | CPUアドレスバス          |

| 22   | CI    | 0              | ROM/SRAM/FDC/VDPアドレスバス                          | 65   | Vcc      | -    | +5V                |

| 23   | CO    | 0              | ROM/SRAM/FDC/VDP                                | 66   | A9       | 1    | CPUアドレスバス          |

| 23   | CU    | 0              | /OPLLアドレスバス                                     | 67   | AI5      | 1    | CPUアドレスパス          |

| 24   | ROM0  | 0              | ROM0チップセレクト信号                                   | 68   | PRST     | 0    | RESET出力            |

| 25   | ROMI  | 0              | ROMIチップセレクト信号                                   | 69   | PDB0     | 0    | ブリンタデータ出力          |

| 26   | ROM2  | 0              | ROM2チップセレクト信号                                   | 70   | PDB1     | 0    | プリンタデータ出力          |

| 27   | RAMI  | 0              | RAMIチップセレクト信号                                   | 71   | PDB2     | 0    | ブリンタデータ出力          |

| 28   | GND   | T -            | GND-                                            | 72   | PDB3     | 0    | プリンタデータ出力          |

| 29   | RAM0  | 0              | RAM0チップセレクト信号                                   | 73   | PDB4     | 0    | ブリンタデータ出力          |

| 30   | LEDI  | 0              | 連射LED出力!、オープンドレイン出力                             | 74   | PD87     | 0    | ブリンタデータ出力          |

| 31   | LED2  | 0              | 連射LED出力 2、オーブンドレイン出力                            | 75   | PDB5     | 0    | プリンタデータ出力          |

| 20   | DEN   | 1/0            | 連射ポリューム回路接続                                     | 76   | PDB6     | 0    | プリンタデータ出力          |

| 32   | REN   | 1/0            | CMOSシュミット入力                                     | 77   | MOUT     | 0    | FDDモターON出力         |

| 33   | SOFT  | 1              | 内蔵ソフト切換スイッチ接続                                   | 78   | GND      | -    | GND                |

| 34   | RST   | 1              | RESET入力信号、CMOSシュミット入力                           | 79   | MIN      | 1    | FDCモーターON入力        |

| 35   | CLKH  | - 1            | 10.74MHzクロック入力                                  | 80   | NRST     | 0    | RESET反転入力          |

| 36   | CSYNC | 1              | VDP CSYNC信号入力                                   | 81   | FDCS     | 0    | FDCチップセレクト信号       |

| 37   | CLKL  | 1              | 3.58MHzクロック入力                                   | 82   | CSOP     | 0    | OPLLチップセレクト信号      |

| 38   | CSW   | 0              | VDP CSW出力                                       | 83   | PTRIGAI  | 1/0  | PORTI TRIGAI信号     |

| 39   | CSR   | 0              | VDP CSR出力                                       | 84   | SITRIGAI | 0    | SI TRIGAI信号        |

| 40   | GND   | _              | GND                                             | 85   | SITRIGA2 | 0    | SI TRIA信号          |

| 41   | D0 .  | 1/0            | CPUデータパス                                        | 86   | CLKX     | 0    | 3.58/5.37MHzクロック出力 |

| 42   | DI    | 1/0            | CPUデータバス                                        | 87   | BUSAK    | 1    | CPUパスアクノリッジ信号      |

| 43   | D2    | 1/0            | CPUデータバス                                        | 88   | WAIT     | 0    | CPUウエイト信号          |

| 44   | D3    | 1/0            | CPUデータバス                                        | _ 00 |          |      | オープンドレイン出力         |

| 45   | D4    | 1/0            | CPUデータバス                                        | 89   | RFSH     | 1    | CPUリフレッシュ信号        |

| 46   |       | 1/0            | CPUデータバス                                        | 90   | MI       | 1    | CPUMIサイクル信号        |

| 47   | D6    | 1/0            |                                                 | 91   | GND      | _    | GND                |

| 48   | D7    | 1/0            |                                                 | 92   | WR       | 1    | CPUライト信号           |

| 49   | CLK4  | 0              | 3.58MHzクロック出力                                   | 93   | RD       | 1    | CPUリード信号           |

| 50   | A5    | 1              | CPUアドレスバス                                       | 94   | IORQ     | 1    | CPUI/Oリクエスト信号      |

| 51   | A4    | T              | CPUアドレスバス                                       | 95   | MREQ     | 1    | CPUメモリーリクエスト信号     |

| 52   | A3    | 1              | CPUアドレスバス                                       | 96   | VSYNC    | 0    | 垂直同期信号             |

| 53   | GND   | <del>  -</del> | GND                                             | 97   | SIX0     | 0    | SI X0出力            |

| 54   | A2    | +              | CPUアドレスバス                                       | 98   | KBX0     | 1    | キーボード X0入力         |

| 55   | AI    | +;             | CPUアドレスバス                                       | 99   | YII.     | 0    | キーボード YII出力        |

| 33   | A0    | +;             | CPUアドレスバス                                       | 100  | PTRIGA2  | 1/0  | PORT2 TRIGA2信号     |