# MSX Computer CX-5M, YIS503F

### SERVICE MANUAL

| ■ CONTENTS                     |                                   |

|--------------------------------|-----------------------------------|

| SPECIFICATIONS 1               | OPERATION OF CARTRIDGE            |

| MSX DESCRIPTION OF OPERATION 3 | PROTECTION25                      |

| MSX BASIC INTERPRETER'S SLOT   | WIRING BLOCK DIAGRAM26            |

| MANAGEMENT MECHANISM 7         | KEYBOARD MATRIX TABLE             |

| DISASSEMBLY PROCEDURES10       | Power Sub Circuit Board & Diagram |

| LSI DATA TABLE11               | Key Sub Circuit Board27           |

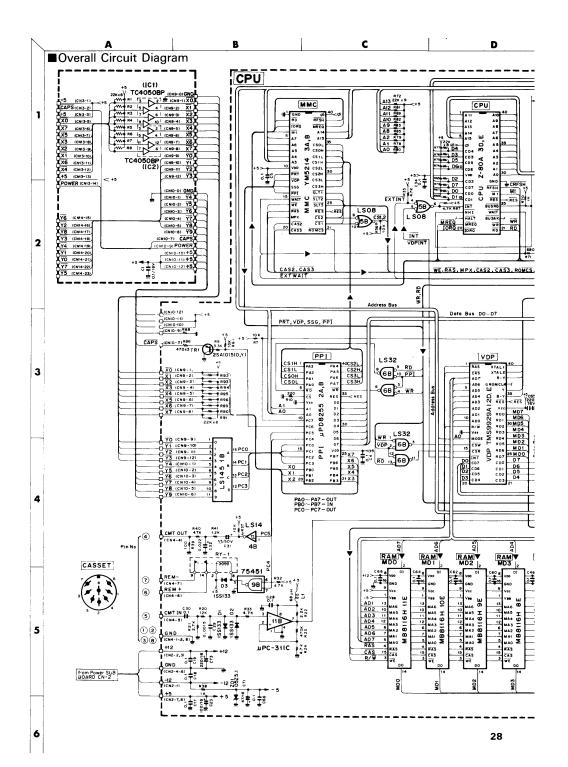

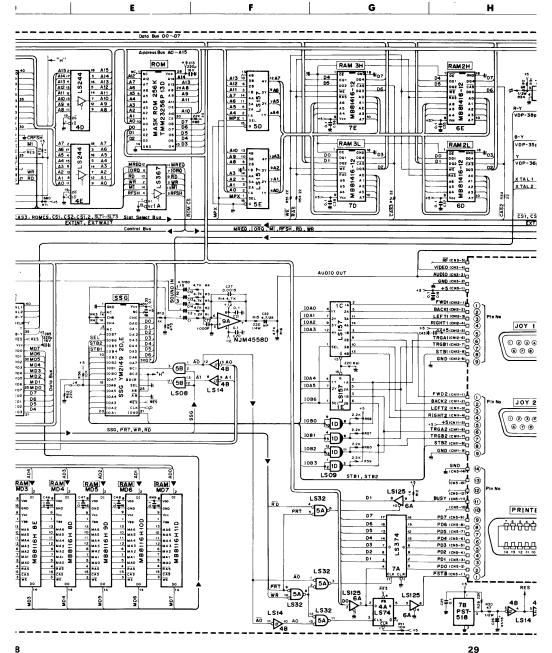

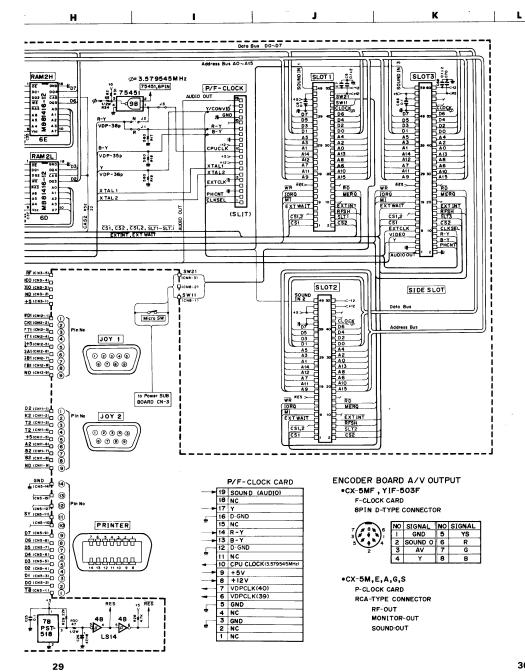

| IC BLOCK DIAGRAM               | Overall Circuit Diagram28         |

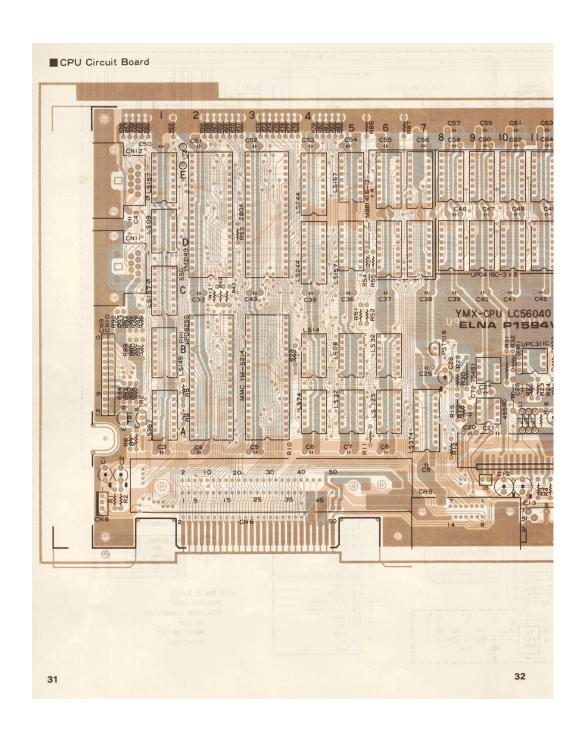

| RGB Circuit Diagram            | CPU Circuit Board31               |

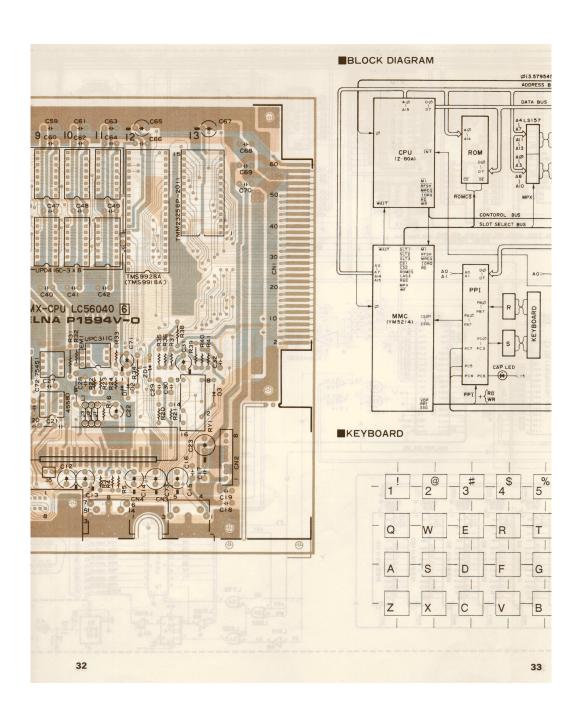

| ENCODER & CLOCK CARD           | BLOCK DIAGRAM                     |

| Circuit Diagram20              | KEYBOARD32                        |

| Power Supply Circuit Diagram   | PARTS LIST                        |

008041

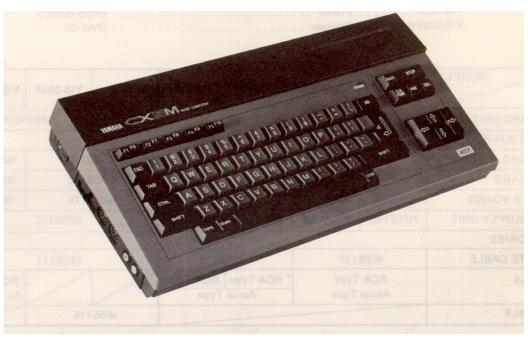

#### YAMAHA MSX COMPUTER ACCORDING TO AREA

There are 7 different model of the YAMAHA MSX computer according to area. This manual refer to the computer as only the CX5M, referring to all models. Where reference to a particular model is called for, the specific model number pertaining to the area in question will be used. The different model numbers, and the area to which they pertain, are as follows:

| CX5ME     | United Kingdom                      | (PAL-I)      |

|-----------|-------------------------------------|--------------|

| CX5MA     | Australia and New Zealand           | (PAL-B)      |

| CX5MG     | West Germany and European Countries | (SECAM)      |

| CX5MS     | Scandinavian Countries              | (SECAM)      |

| CX5MF     | France                              | (RGB output) |

| YIS-503F  | France                              | (RGB output) |

| YIS-503FB | Belgium                             | (PAL-G)      |

| MODEL             |                 |         |                     |         |         |          |             |

|-------------------|-----------------|---------|---------------------|---------|---------|----------|-------------|

| UNIT              | CX5ME           | CX5MA   | CX5MG               | CX5MS   | CX5MF   | YIS-503F | YIS-503FB   |

| KEYBOARD UNIT     |                 | •       | PB55070             |         | •       | PB5      | 5079        |

| KEY SUB BOARD     |                 |         |                     | NA55171 |         |          |             |

| CPU BOARD         |                 | NA5     | 5169                |         | NA5     | 5170     | NA55169     |

| CLOCK CARD        | NA55174 NA55170 |         |                     |         |         |          | NA55174     |

| ENCODER BOARD     | PB55077         | PB55076 | PB5                 | 5078    | NA55176 |          | PB55075     |

| POWER SUPPLY UNIT | NP55140         | NP55150 | NP55180             | NP55130 |         | NP55170  | •           |

| ACCESSORIES       |                 |         | •                   |         |         |          |             |

| CASSETTE CABLE    | Mi55            | 5117    | * Mis               | 5116    | Mi55117 |          |             |

| RF CABLE          | RCA Type        |         | * RCA Type RCA Type |         |         |          | RCA Type    |

|                   | Aerial          | Туре    | Aerial Type         |         | \       |          | Aerial Type |

| RGB CABLE         |                 |         |                     |         | Mi55    | 115      |             |

<sup>\*</sup> marked : with Core

#### • SPECIFICATIONS

| CPU                      |                                                                  | CRT DISPLAY       |                                                                                         |

|--------------------------|------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|

| CPU                      | : Z80A compatible                                                | Video Display     |                                                                                         |

| Clock                    | : 3.579545 MHz                                                   | Processor (VDP)   | : TMS9929A                                                                              |

| Wait<br>Interrupt        | : 1 wait in M1 cycle<br>: INT enternal and VDP, NMI inter-       | Fonts             | : Alpha-numerics, graphic patterns other patterns in 8 X 8 dots                         |

|                          | rupt non used. (In MSX-BASIC inter-                              | Color             | : 16 colors                                                                             |

|                          | preter 50Hz signal from VDP is used for the interrupt.) (MODE 1) | Display capabilit | ey: When power is turned on, 37 characters per line X 24 lines                          |

| Reset                    | : Power on reset                                                 |                   | Possible upto 40 characters per line by software control                                |

| MEMORY                   |                                                                  | Resolution        | : 256 dots x 192 lines (non-interlace)                                                  |

| Main memory<br>Video RAM | : 32 KB (MB81416-12X4)<br>: 16KB (μPD416C-3X8)                   | I/O INTERFACE     |                                                                                         |

| ROM                      | : 32KB (MSX-BASIC international version)                         | Keyboard          | : Stroke type step sculpture<br>Alpha numeric characters,<br>special characters and     |

|                          |                                                                  |                   | Alpha numeric characters 48  Control and special effect keys 16  Cursor movement keys 4 |

Function keys (programmable) . . 5 CAPS lock keys with LED indication

Audio Cassette Interface

: 8 pin DIN connector

Baut rate 1200/2400 BPS switchable

be software FSK standard

With remote control (Cassette motor

ON/OFF)

Printer Interface: 8 bit parallel centronics standard

TTL level signal

14 pin connector

Universal I/O

Interface

(JOYSTIC etc.) : 2 ports

9 pin type D connector (male) X 2

TTL level

Audio/Video Output

: [CX-5ME, A, G, S, YIS-503FB]

1) MONITOR output

PAL composite video output 75 $\Omega$

2) SOUND output

8 octaves/3 tones + noise SSG is YM-2149

Beep Sound (PPI: μPD8255C-5)

3) RF output

G-PAL (UHF, 36ch) . .CX5MG,

CX5MS, YIS-503FB

B-PAL (VHF, 3ch, 4ch).CX5MA I-PAL (UHF, 36ch) . . . CX5ME

: [CX5MF, YIS-503F]

1) MONITOR output

RGB output

8 pin DIN connector

Upper Slot

(SLOT #1) : 50 pins MSX standard female con-

nector

Rear Slot (SLOT #2)

: 50 pins card edge connector

Side Slot (SLOT #3)

: 60 pins card edge connector

POWER SUPPLY UNIT CAPACITY

+5V ± 5% 1.9A

Slots

300mA X 2

Universal I/O ports

50mA X 2

A/V output

50mA

+12V ± 10% 0.5A (max) -12V ±10% 0.16A (max)

**GENERAL SPECIFICATIONS**

Power supply: [CX5MF, G, S, YIS503F, FB]

AC220V ± 10% [CX5ME, A] AC240V ± 10%

Power input: 30 watts maximum

Measurement: 423(W) x 208(D) x 68(H) mm (CPU)

245(W) x 100(D) x 68(H) mm (Power

Supply Unit)

2.8 kg (CPU)

1.0 kg (Power Supply Unit)

**ACCESSORIES**

Weight:

Cassette interface cable:

CPU side . . DIN 8 pin plug Cassette recorder side:

Earphone plug (White) . . . . Mini plug (3.5¢)

Mic plug (Red) . . . . Mini plug (3,5¢)

Rem-Control plug (Black). . . Mini plug  $(3.5\phi)$

Length: 1 m

RF cable: Length . . . . 2 m (CX5ME, A, S,

YIS503FB)

Length . . . . 0.98 m (CX5MG)

RGB cable: Length . . . 1.5 m (CX5MF)

#### • DISPLAY MODE

| MODE        |        | Resolution | Size       | Number | Specified<br>Color | Sprite        | Characters           |

|-------------|--------|------------|------------|--------|--------------------|---------------|----------------------|

| Graphic I   | MAX    | 256 X 192  | 8 X 8      | 256    | 16 colors          | Possibility   | 32 X 24              |

| (Screen 1)  | NORMAL | 240 X 192  |            | 250    | 10 colors          | Tossibility   | 29 X 24              |

| Graphic II  | MAX    | 256 X 192  | 8 X 8      | 768    | 16 colors          | Possibility   | 32 X 24              |

| (Screen 2)  | NORMAL | 240 X 192  |            | /00    | 70 001013          | 1 Ossibility  | 29 X 24              |

| Multi Color | MAX    | 64 X 40blk | 4 X 4      | _      | 16 colors          | Possibility   | 8 X 6                |

| (Screen 3)  | NORMAL | 60 X 40blk | per 1block | _      | 16 colors          | Possibility   | 0.0                  |

| TEXT        | MAX    | 256 X 192  | 8 X 6      | 256    | 2 out of 16        | Impossibility | 40 X 29              |

| (Screen 0)  | NORMAL | 240 X 192  |            | 256    | colors             | Impossibility | 39 X 24<br>37 X 24** |

<sup>\*\*</sup>USE VDP (TMS9929A)

#### • MSX DESCRIPTION OF OPERATION

#### CPU (Z80A)

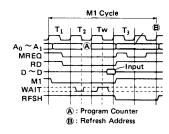

A 3.579545 MHz system clock is fed to the CPU from clock card. Thus one machine cycle is approximately 279 ms. Address bus (16 bits), data bus (8 bits), control bus (6 bits) and other control lines are connected to peripheral devices and units.

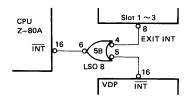

The one machine cycle WAIT is inserted per each M1 cycle (instruction fetch cycle). WAIT can be inserted through slots 1  $\sim$  3 are logically ORed and led to INT line. 50 Hz interrupt signal in output from VDP to initiate each 1/50 second for the screen control or keyboard scan.

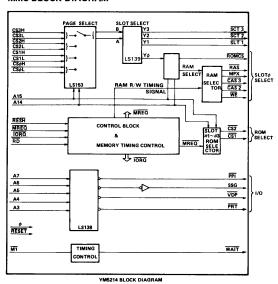

#### MMC (YM-5214)

It is a dedicated LSI for MSX and developed by YAMAHA.

Based on the MSX specifications it handles the memory bank select, standard I/O control, various access timing generation for ROM and RAM or M1 WAIT instruction generation.

#### MMC BLOCK DIAGRAM

3

#### VDP (TMS9929A)

50 Hz interrupt signal in output from VDP.

It supports 16 Kbytes of V-RAM. It produces a PAL video signal for TV display according to the CPU instructions.

#### SSG (YM-2149)

It is compatible to General Instrument's PSG (AY3-8910) and enhanced.

Designed and developed by YAMAHA.

It produces by program 3 notes and a noise and provided with two 8 bits universal I/O ports for joystick and other peripherals.

#### PPI (μPD8255AC-5)

Three 8 bits universal I/O ports A, B and C are provided.

Each port may be controlled by software and the following functions are assigned as a specification.

Port A: Memory bank signal output.

Port B: Keyboard scan signal input

Port C: Keyboard strobe signal output, CAPS lock LED switch, cassette data recorder control, etc.

#### • Memory map and slot

Memory Map and Slot

ROM: 32K bytes MSX BASIC ROM on slot 0, address 0000H  $\sim$  7FFFH.

RAM: DRAM of 16K bytes X 2 (total of 32K bytes) on slot 0, address 8000H  $\sim$  FFFFH.

|       | Slot 0    | Slot 1 | Slot 2 | Slot 3 |

|-------|-----------|--------|--------|--------|

| FFFFH | RAM 16Kb  |        |        |        |

| С000Н | RAM 16Kb  |        |        |        |

| 8000Н | MSX BASIC |        |        |        |

| 4000Н | ROM 32Kb  |        |        |        |

| 0000H |           |        | L      | L      |

(Memory Map

VRAM: 16 Kbytes V-RAM are is separated from the system bus and is supported by VDP.

#### SLOT SELECT SIGNAL OF PPI PORT A

PPI-A8H-PORT

| PPI PORT A |   | RTA                                                             |   |       |   |  |  |

|------------|---|-----------------------------------------------------------------|---|-------|---|--|--|

| CS0        | L | Specified bit to select 0000H ∼ 3FFFH                           |   | LSB   | 0 |  |  |

| CSU        | Н | area from which SLOT                                            |   | bit 1 | 0 |  |  |

| CS1        | L | Specified bit to calcut 4000H ~ 7555H                           |   | bit 2 | 0 |  |  |

| CSI        | Н | Specified bit to select 4000H ~ 7FFFH area form which SLOT      |   | bit 3 | 0 |  |  |

| CS2        | L | Considered bit to select 9000H or REEEH                         |   | bit 4 | 0 |  |  |

| CSZ        | Н | Specified bit to select 8000H $\sim$ BFFFH area from which SLOT |   | bit 5 | 0 |  |  |

| CS3        | L | Considered his to relate COCOLL or EEEELL                       | T | bit 6 | 0 |  |  |

| US3        | Н | Specified bit to select C000H ~ FFFFH area from which SLOT      |   | MSB   | 0 |  |  |

MSX BASIC MODE

#### SLOT SPECIFICATION BY EACH CSX L, H (X = 0, 1, 2, 3)

| 1 | L/H  | 0/0      | 1/0    | 0/1    | 1/1    |

|---|------|----------|--------|--------|--------|

|   | Slot | ROM, RAM | Slot 1 | Slot 2 | Slot 3 |

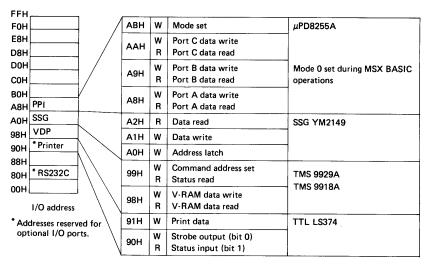

#### • I/O port address map

According to the MSX specifications, the 256 byte Z-80A I/O port area from 00H to FFH is reserved for the standard MSX system devices as follows:

#### PPI input/output port

When MSX-BASIC is operating, the mode is set to MODE 0 (PA0 ~ PA7, PB0 ~ PB7 and PC0 ~ PC7 can be controlled as 8-bit port independently.) and each port controls the following input/output.

PA0 ~ PA7: Output port to MMC, sends out data to produce slot select signal.

PB0 ~ PB7: Input port of keyboard scanning data.

PC0 ~ PC3: Sends scanning signal to keyboard through LS145.

PC4: (Motor ON/OFF control data recorder (cassette) Turns relay ON at "L".

PC5: Output FSK specification data to data recorder (cassette).

PC6: LED lights at CAPS lock LED "L".

PC7: Emits beeping sound through 1 bit output.

#### SSG input/output port

This LSI produces the programmable triple chord scale as well as noise, and at the same time, controls the next input/ output unit by means of the two input/output port.

${\sf CHA} \sim {\sf CHC}$ : Triple chord output terminal and noise output terminal.

IOA0 ~ IOA5: Input port of general purpose input/output port (JOYSTICK 1, 2) scanning data.

LED lights at CODE lock LED "L"

IOA7: Input port for data from data recorder (cassette).

IOB0 ~ IOB6: General purpose input/output port (JOYSTICK 1, 2) select and strobe & scanning.

**IOB0** ∼ **IOB3**: Port scanning data output

IOB4: JOY 1 strobe signal output IOB5: JOY 2 strobe signal output

IOB6: JOY 1, 2 select signal

IOB "L" . . . . . JOY 1 select IOB "H" . . . . . . JOY 2 select

IOB7: Non-Used

The specified functions of PPI and SSG input/output ports as described above are all set by the inner monitor when power ON reset and MSX-BASIC in operation (without anything inserted in the slot).

#### SLOTs #1 and #2 PIN ASSIGNMENT

| Pin<br>No. | Pin Name   | 1/0 | Description                                                                        |

|------------|------------|-----|------------------------------------------------------------------------------------|

| 1          | CS1        | 0   | Select Signal for ROM 4000H-7FFFH                                                  |

| 2          | CS2        | 0   | Select Signal for ROM 8000H-BFFFH                                                  |

| 3          | CS1, 2     | 0   | Select Signal for ROM 4000H-BFFFH                                                  |

| 4          | SLTSL      | 0   | Slot Select Signal                                                                 |

| 5          | N/C        | _   | Inhibited to use                                                                   |

| 6          | RFSH       | 0   | Dinamic RAM refresh signal                                                         |

| 7          | EXT WAIT   | 4   | WAIT request, open collector signal                                                |

| 8          | EXT INT    | - 1 | Maskable interrupt request, open collector signal                                  |

| 9          | M1         | 0   | M1 signal from CPU                                                                 |

| 10         | BUSDIR     | - 1 | Direction Control for external Bus Buffer                                          |

| 11         | IORQ       | 0   | I/O request from CPU                                                               |

| 12         | MERQ       | 0   | Internal memory request from CPU                                                   |

| 13         | WR         | 0   | Write request from CPU                                                             |

| 14         | RD         | 0   | Road request from CPU                                                              |

| 15         | RES        | 0   | System Preset signal                                                               |

| 16         | N/C        | _   | Inhibited to use                                                                   |

| 17         | A9         | 0   |                                                                                    |

| 18         | A15        | 0   |                                                                                    |

| 19         | A11        | 0   |                                                                                    |

| 20         | A10        | 0   |                                                                                    |

| 21         | A7         | 0   |                                                                                    |

| 22         | A6<br>A12  | 0   |                                                                                    |

| 23         |            | 0   |                                                                                    |

| 24<br>25   | A8<br>A14  | 0   | Address Bus signal                                                                 |

| 26         | A14<br>A13 | 0   | Address Bus signal                                                                 |

| 27         | A13        | 0   |                                                                                    |

| 28         | A0         | 0   |                                                                                    |

| 29         | A3         | ő   |                                                                                    |

| 30         | A2         | ő   |                                                                                    |

| 31         | A5         | ŏ   |                                                                                    |

| 32         | A4         | ō   | IJ                                                                                 |

| 33         | D1         | 1/0 | <u> </u>                                                                           |

| 34         | D0         | 1/0 |                                                                                    |

| 35         | D3         | 1/0 |                                                                                    |

| 36         | D2         | 1/0 | Data Bus signal                                                                    |

| 37         | D5         | 1/0 |                                                                                    |

| 38         | D4         | 1/0 |                                                                                    |

| 39         | D7         | 1/0 |                                                                                    |

| 40         | D6         | 1/0 | J                                                                                  |

| 41         | GND        | -   | Ground                                                                             |

| 42         | CLOCK      | 0   | System Clock 3,579545MHz                                                           |

| 43         | GND        | -   | Ground                                                                             |

| 44         | SW13       | -   | System protection                                                                  |

| 45         | +5         | _   | Power Supply +5V                                                                   |

| 46         | SW2        | _   | System protection (Note: SW1 and SW2 is in connection when Cartridge is inserted.) |

| 47         | +5         | -   | Power Supply +5V                                                                   |

| 48         | +12        | -   | Power Supply +12V                                                                  |

| 49         | SOUND IN   | 1   | Sound input line (-5dbm) mixed with PSG sound and output                           |

| 50         | -12        |     | Power Supply –12V                                                                  |

#### SLOT #3 PIN ASSIGNMENT

| Pin<br>No. | Pin Name      | 1/0   | Description                            |  |

|------------|---------------|-------|----------------------------------------|--|

| 1          | SOUND OUT     | 0     | Mixing Sound out of SSG, PP1           |  |

| 2          | GND           | -     | Ground                                 |  |

| 3          | GND           | l – 1 | Ground                                 |  |

| 4          | PHASE CONTROL | 1     | Control signal Input for superimpose   |  |

| 5          | Y             | 0     | Brightness signal from TMS-9928A       |  |

| 6          | B-Y           | 0     | Color difference signal from TMS-9928A |  |

| 7          | C-VIDEO       | 0     | Color difference signal from TMS-9928A |  |

| 8          | R-Y           | 0     | Color difference signal fro TMS-9928A  |  |

| 9          | EXT CLOCK     | 1     | External clock input for superimpose   |  |

| 10         | CLOCK INT/EX  | 1     | Clock selector for superimpose         |  |

| 11~60      |               |       | Exactly same as regular slot           |  |

Note) Side slot dedicated pins are only applicable to the model equipped with the TMS 9929A VDP. But non used

#### •MSX BASIC interpreter's slot management mechanism

#### Memory structure of MSX

|    | #0 (SLOT 0) |      | #0 (SLOT 0) #1 (UPPER SLO |         |          |   | Γ) | #2 (REAR SLOT) |        |     |  | #3 (SIDE SLOT) |       |      |

|----|-------------|------|---------------------------|---------|----------|---|----|----------------|--------|-----|--|----------------|-------|------|

| ı  |             | expa | nded                      |         | expanded |   |    |                | expand | ded |  |                | expar | nded |

|    | Primary     | L    |                           | Primary |          |   |    | Primary        |        |     |  | Primary        |       |      |

| FH |             |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| он |             |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| FH |             |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| юн |             |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| FH | В           |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| юн | Ä           |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| FH | Ĭ           |      |                           |         |          |   |    |                |        |     |  |                |       |      |

| он | С           |      |                           |         |          | 1 |    |                |        |     |  |                |       |      |

Total: 1024K bytes (16X64K bytes)

Terminology: Primary slot . . . . . . . Slot which is enabled by slot select register within 8255 PPI.

Secondary slot . . . . . . Slot which is enabled by expansion slot register placed at OFFFFH.

Page . . . . . . . . . Block of memory (maximum 16K) in each slot.

A slot is divided into 4 pages.

(0000H to 3FFFH, 4000H to 7FFFH, 8000H to 0BFFFH, 0C000H to 0FFFFH)

#### 1. Minimum configuration

- a) Microsoft MSX BASIC interpreter at slot #0 from 0000H to 7FFFH.

- b) Minimum of 8K RAM from 0E000H to 0FFFH in any slot (including the secondary slot).

#### 2. RAM search procedure

MSX BASIC first searches for available RAM from 0BFFFH down to 8000H (including the ones in secondary slots), then enables the page containing the largest RAM. If there are more than one such pages, selects the leftmost page in the figure above. MSX BASIC next searches for available RAM from 0FFFFH down to 0C000H, and does the same thing described above. Finally, MSX BASIC searches for continuous RAM block from 0FFFFH down to 8000H and sets the system variable "BOTTOM".

#### 3. PROGRAM CARTRIDGE search procedure

MSX BASIC scans all slots (including secondary slots) from 4000H to 0BFFFH for a valid ID at the beginning of each page, collects information, and passes control to each page. The scan order is from left to right in the figure above. The format of ID and others are as follows.

#### • Offset from top

| +0000H  |           |

|---------|-----------|

| +0002H  | ID        |

| +0004H  | INIT      |

| +0006H  | STATEMENT |

| +0008H  | DEVICE    |

| +000AH  | TEXT      |

| 1000411 |           |

|         | reserved  |

| +0010H  |           |

- ID is a 2 byte code used to distinguish ROM cartridges from empty pages. "AB" (41H, 42H) is used for this purpose.

- INIT holds an address of the initialization procedure specific to this cartridge. 0 when no such procedure is necessary.

Programs that need to work co-operatively with BASIC interpreter should return control to it by Z80's "RET" instruction (all registers except [SP] can be destroyed). Other programs (such as game programs) need not to do so, however.

- STATEMENT holds an address of the expanded statement handler if such is contained in this cartridge. 0 when no such handler is inside. When BASIC encounters a 'CALL' statement, it calls this address with the statement name in the system area. Following are the notes to be remembered. (In the notes below, [HL] register pair is called a 'text pointer')

- 1) The cartridge must be placed at 4000H ~ 7FFFH.

- 2) Syntax for expanded statement is,

```

CALL < statement name > [ (< arg > [ , < arg > ] ...) ] Key word "CALL" can be substituted with an under score character, " – ".

```

- 3) Statement name is stroed in the system area terminated by 0. The buffer for statement name is of fixed length (16 bytes) so statement name cannot be longer than 15 characters.

- 4) If the handler for that statement is not inside the cartridge, return with carry flag set. Text pointer must be returned unchanged.

- 5) If the handler for that statement is inside the cartridge, the cartridge should do the function, update text pointer to the end of the statement (usually, pointing to 0 which indicates the end of line, or ": "which indicates the end of statement), and return with carry flat reset (registers except [SP] can be destroyed). At the entry to the expanded statement handler, text pointer is set up to point to the first non-blank character after the statement name.

- DEVICE holds an address of the expanded device handler if such is contained in this cartridge. 0 when no such handler is inside. BASIC calls this address with the device name in the system area. Following are notes to be remembered.

- 1) The cartridge must be placed at 4000H ~ 7FFFH.

- Device name is stored in the system area terminated by 0. The buffer for statement name is of fixed length (16b bytes) so device name cannot be longer than 15 characters.

- 3) A cartridge (16K) can have up to 4 logical devices.

- 4) When BASIC encounters a device name which is not known to itself, it calls DEVICE entry with 0FFH is [Acc]. If the handler for that device is not inside the cartridge, carry should be returned set. If it's inside, device ID (from 0 to 3) should be returned in [Acc], and carry reset. All registers can be destroyed.

- 5) Real I/O operations take place when a DEVICE entry is entered with one of the following values in [Acc].

- 0 Open

- 2 Close

- 4 Random I/O

- 6 Sequential output

- 8 Sequential input

- 10 LOC function

- 12 LOF function

- 14 EOF function

- 16 FPOS function

- 18 Back up a character

Device ID is passed in the system variable "DEVICE".

- TEXT holds the beginning address of BASIC. text contained in the cartridge. 0 when no such text is inside. BASIC regards this as the beginning address of BASIC text, sets pointer there, and begins execution of the program. Following are the notes to be remembered.

- 1) When there are more than one such slots, only the leftmost one (in the figure of Memory structure of MSX above) is enabled and executed.

- 2) The cartridge must be placed at 8000H  $\sim$  0BFFFH, thus the maximum length of BASIC text cannot exceed 16 Kbytes.

- 3) Even if there is a RAM block equipped at 8000H  $\sim$  0BFFFH, it can never be used.

- 4) The address pointed to by the TEXT entry must contain a zero.

- 5) The line numbers (for statements which reference line numbers, such as GOTO, GOSUB, etc.) had better be translated to pointers in advance because they are never converted to pointers when executed. The can be line numbers however, but the execution would become slower then.

NOTE: INIT, STATEMENT, DEVICE and TEST are placed low order byte first.

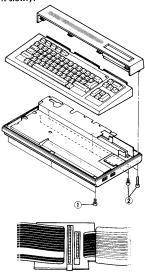

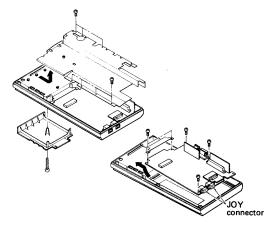

#### DISASSEMBLY PROCEDURES

#### Case removal

- 1) Remove three screws 1 in the bottom case.

- 2) Lift the front end of the keyboard case and remove it.

- 3) Remove five screws 2 in the bottom case and lift the case.

- 4) Disconnect the keyboard cable to the CPU boars by pulling it slowly.

#### Power Sub board and lower shield plate removal

- 1) Remove two screws and remove the power sub board and power switch,

- 2) Remove one screw, move the lower shield plate to the left and remove it by lifting it up.

#### CPU board removal

- 1) Remove seven screws, move the shield plate to the right a little and lift it up.

- 2) Remove three connectors of the CPU board.

- 3) Remove the side slot connector cover shield plate.

- 4) Remove three screws, lift the slotted side and pull to the left. Then remove the JOYSTICK connector from the bottom case and remove the CPU boards by lifting it up.

#### • LSI DATA TABLE

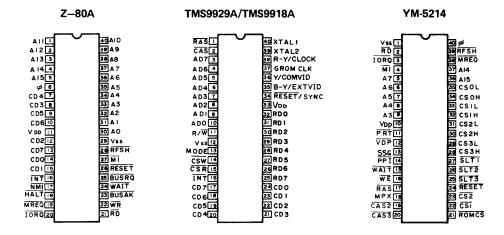

#### CPU (Z80A)

| Pin No. | Pin Name                             | 1/0 | Active | Function                                                                                                                                                                                                                   |

|---------|--------------------------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~5     | A11, 12, 13, 14, 15                  | 0   |        | Address bus                                                                                                                                                                                                                |

| 6       | φ                                    | ı   |        | 3.579545 MHz clock input                                                                                                                                                                                                   |

| 7 ~ 10  | CD4, 3, 5, 6                         | 1/0 |        | Data bus                                                                                                                                                                                                                   |

| 11      | VDD                                  | 1   |        | Voltage Supply +5V                                                                                                                                                                                                         |

| 12 ~ 15 | CD2, 7, 0, 1                         | 1/0 |        | Data bus                                                                                                                                                                                                                   |

| 16      | INT                                  | l   | L .    | Mask-able interrupt input pin: Mode 1 is used for inter-<br>rupt which is input by taking the logic OR of the VDP<br>interrupt output (every 1/60s.) and the cartridge<br>interrupt input (EXT INT) (when using MSX-BASIC) |

| 17      | NMI                                  |     |        | Non-connect                                                                                                                                                                                                                |

| 18      | HALT                                 |     |        | Non-connect                                                                                                                                                                                                                |

| 19      | MREQ                                 | 0   | L      | Active when the effective address for memory access is on the address bus.                                                                                                                                                 |

| 20      | IORQ                                 | О   | L      | Active when the effective address for the input/output port access is on the address bus (also active when in INT or ACK cycle)                                                                                            |

| 21      | RD                                   | 0   | L      | Active during the period when the CPU can receive data from the memory and input/output port.                                                                                                                              |

| 22      | WR                                   | О   | L      | Active when the CPU sends data to be stored in the memory and input/output port to the data bus.                                                                                                                           |

| 23      | BUSAK                                |     |        | Non-connect                                                                                                                                                                                                                |

| 24      | WAIT                                 | l   | L      | CPU remains in the wait state as long as this signal is active "L". (No refresh signal is generated when in the WAIT state.)                                                                                               |

| 25      | BUSRO                                |     |        | Non-connect                                                                                                                                                                                                                |

| 26      | RESET                                | ı   | L      | The program counter becomes "0" at the RESET input and the CPU is initialized.                                                                                                                                             |

| 27      | M1                                   | 0   | L      | One "L" pulse is output at each instruction fetch cycle (also active when in the INT or ACK cycle)                                                                                                                         |

| 28      | RFSH                                 | 0   | L      | Active when the low order 7 bit refresh address for D-RAM is on the address bus                                                                                                                                            |

| 29      | Vss                                  | ı   |        | Ground                                                                                                                                                                                                                     |

| 30 ~ 40 | A0, 1, 2, 3, 4, 5, 6,<br>7, 8, 9, 10 | 0   |        | Address bus                                                                                                                                                                                                                |

#### MEMORY CONTROLLER (YM-5214)

| Pin No. | CONTROLLER (YM  | 1/0 | Active | Function                                                     |

|---------|-----------------|-----|--------|--------------------------------------------------------------|

| 1       | Vss             | 1   |        | Ground                                                       |

| 2       | RD              | 1   | L      | CPU (Z80A) RD signal input                                   |

| 3       | IORQ            | 1   | L      | CPU (Z80A) IORQ signal input                                 |

| 4       | M1              | 1   | L      | CPU (Z80A) M1 signal input                                   |

| 5~9     | AD7, 6, 5, 4, 3 | 1   |        | CPU (Z80A) address 7 ~ 3 signal input                        |

| 10      | VDD             |     |        | Voltage Supply +5V                                           |

| 11      | PRT             | 0   | L      | Printer interface port select                                |

| 12      | VDP             | 0   | L      | VDP port select                                              |

| 13      | SSG             | 0   | н      | SSG port select                                              |

| 14      | PPI             | 0   | L      | PPI port select                                              |

| 15      | WAIT            | 0   | L      | 1 WAIT signal generated in M1 cycle                          |

| 16      | WE              | 0   | L      | D-RAM WE signal                                              |

| 17      | RAS             | 0   | L      | D-RAM RAS signal, RAS only refresh function by Z80A provided |

| 18      | MPX             | О   | н      | D-RAM address multiplex signal                               |

| 19      | CAS2            | О   | L      | D-RAM (SLOT# 0,8000H-BFFFH) CAS signal                       |

| 20      | CAS3            | О   | L      | D-RAM (SLOT # 0,C000H-FFFFH) CAS signal                      |

| 21      | ROMCS           | 0   | L      | MSX-BASIC ROM select signal                                  |

| 22      | CS1             | 0   | L      | ROM 4000H-7FFFH select signal                                |

| 23      | CS2             | 0   | L      | ROM 8000H-BFFFH select signal                                |

| 24      | RESET           | 1   | L      | SYSTEM RESET signal input                                    |

| 25      | SLT3            | 0   | L      | SLOT #3 select signal                                        |

| 26      | SLT2            | 0   | L      | SLOT #2 select signal                                        |

| 27      | SLT1            | 0   | L      | SLOT #1 select signal                                        |

| 28      | CS3H            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 29      | CS3L            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 30      | CS2H            | 4   |        | Slot select register (PPI PORT—A) signal                     |

| 31      | CS2L            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 32      | CS1H            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 33      | CS1L            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 34      | CS0H            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 35      | CS0L            | 1   |        | Slot select register (PPI PORT—A) signal                     |

| 36, 37  | A15, A14        | 1   |        | CPU (Z80A) ADDRESS 15, 14 signal input                       |

| 38      | MREQ            | 1   | L      | CPU (Z80A) MREQ signal input                                 |

| 39      | RFSH            | 1   | L      | CPU (Z80A) RFSH signal input                                 |

| 40      | φ               | 1   |        | CPU (Z80A) CLOCK signal input                                |

VDP Video Display Processor (TMS9929A/TMS9918A)

| Pin No. | Pin Name                          | I/O | Active | Function                                                                                                                        |

|---------|-----------------------------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------|

| 1       | RAS                               | 0   | L      | Low address strobe                                                                                                              |

| 2       | CAS                               | 0   |        | VRAM column address strobe                                                                                                      |

| 3 ~ 10  | AD7, 6, 5, 4, 3, 2,<br>1, 0 (MSB) | 0   |        | VRAM address and data bus (VRAM low and column<br>address and data multiplexed and output) (AD0 is the<br>most significant bit) |

| 11      | R/W                               | 0   | H=read | VRAM write strobe                                                                                                               |

| 12      | Vss                               | ı   |        | Ground                                                                                                                          |

| 13      | MODE                              | 1   |        | CPU interface mode select                                                                                                       |

| 14      | CSW                               | 1   | L      | Write strobe                                                                                                                    |

| 15      | CSR                               | I   | L      | Read strobe                                                                                                                     |

| 16      | INT                               | 0   |        | Interrupt signal to CPU                                                                                                         |

| 17 ~ 24 | CD7, 6, 5, 4, 3, 2,<br>1, 0 (MSB) | I/O |        | CPU data bus (CDO is the most significant bit) CPU data bus (CDO is the most significant bit)                                   |

| 25 ~ 32 | RD7, 6, 5, 4, 3, 2<br>1, 0 (MSB)  | I   |        | VRAM read data bus (RDO is the most significant bit)                                                                            |

| 33      | Voo                               | 1   |        | Voltage Supply +5V                                                                                                              |

| 34      | RESET/SYNC                        | I   |        | 3-level input pin (less than 0.6V: RESET active → VDP initialized, over 10V:SYNC active → VDP synchronized externally)          |

| 35      | B-Y/EXTVID                        | 0   |        | B-Y color signal out/external video signal input                                                                                |

| 36      | Y/COMVID                          | 0   |        | Y signal out (brightness and synchronous composite video signal)                                                                |

| 37      | GROMCLK                           | О   |        | Output of quartz oscillator (or external clock) signal frequency divided by 24 (ordinarily not used)                            |

| 38      | R-Y/CLOCK                         | 0   |        | R−Y color signal out/clock φ output                                                                                             |

| 39      | XTAL2                             | 1   |        | Quartz oscillator connecting terminal                                                                                           |

| 40      | XTAL1                             |     |        | (10.73864MHz) (When driving external clock, drive both inputs)                                                                  |

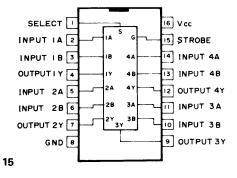

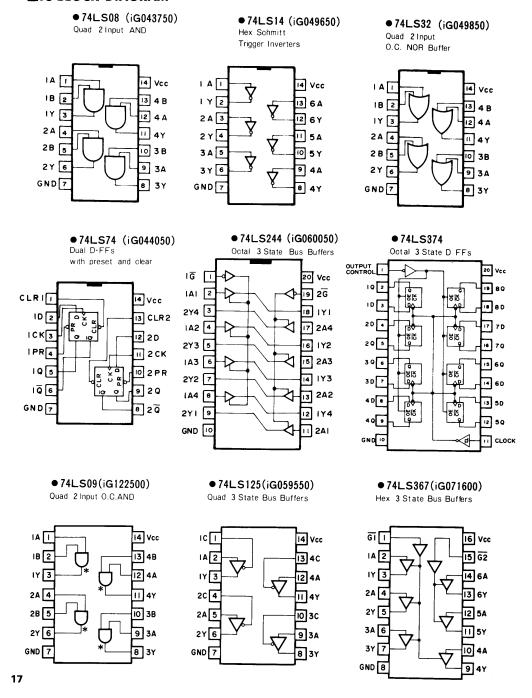

# ● 74LS145 (iG12410) O.C.BCD to DECIMAL Decorder/Driver

16 Vcc 15 A BC.D-TO-DECIMAL 14 B 2 3 INPUT OUTPUT 13 C 3 4 12 D 108 OUTPUT 9 7

#### SSG Sound Generator (YM-2149)

| Pin No. | Pin Names                    | 1/0 | Active | Function                                                       |

|---------|------------------------------|-----|--------|----------------------------------------------------------------|

| 1       | Vss                          |     |        | Ground                                                         |

| 2       | NC                           |     |        | Non-connect                                                    |

| 3, 4    | ANALOG CHANNEL<br>B, A       | 0   |        | Output of D/A converter                                        |

| 5       | NC                           |     |        | Non-connect                                                    |

| 6~13    | IOB7, 6, 5, 4, 3,<br>2, 1, 0 | I/O |        | Parallel data 8 bit port input/output                          |

| 14 ~ 21 | IOA7, 6, 5, 4, 3,<br>2, 1, 0 | I/O |        | Parallel data 8 bit port input/output                          |

| 22      | CLOCK                        | ı   |        | Supplies reference time for tone, noise and envelope generator |

| 23      | RESET                        | 1   |        | RESET input                                                    |

| 24      | A9                           | ı   |        | Fixed to "L"                                                   |

| 25      | A8                           | ı   |        | Fixed to "H"                                                   |

| 26      | SEL                          |     |        | Selection of CLOCK frequency                                   |

| 27      | BDIR                         | 1   |        | Internal operation control command                             |

| 28, 29  | BC2, BC1                     | ı   |        | signal                                                         |

| 30 ~ 37 | DA7, 6, 5, 4, 3, 2,<br>1, 0  | I/O |        | Data input/output                                              |

| 38      | ANALOG CHANNEL<br>C          | 0   |        | Output of D/A converter                                        |

| 39      | TEST1                        |     |        | Test pin                                                       |

| 40      | VDD                          |     |        | Voltage Supply +5V                                             |

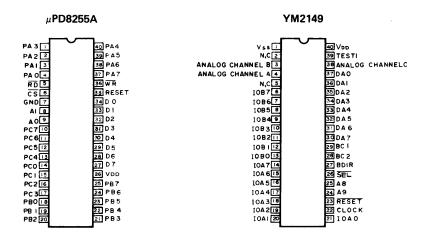

#### PPI (μPD8255A)

| Pin No. | Pin Name                    | I/O | Active | Function                              |  |

|---------|-----------------------------|-----|--------|---------------------------------------|--|

| 1~4     | PA3, 2, 1, 0                |     |        | Port A (BIT)                          |  |

| 5       | RD                          | 1   |        | Read input                            |  |

| 6       | <del>cs</del>               |     |        | Chip select                           |  |

| 7       | GND                         |     |        | Ground                                |  |

| 8, 9    | A1, A0                      |     |        | Internal register select signal input |  |

| 10~17   | PC7, 6, 5, 4, 0, 1,<br>2, 3 |     |        | Port C (BIT)                          |  |

| 18 ~ 25 | PB0, 1, 2, 3, 4, 5,<br>6, 7 |     |        | Port B (BIT)                          |  |

| 26      | VDD                         |     |        | Power Supply +5V                      |  |

| 27 ~ 34 | D7, 6, 5, 4, 3, 2,<br>1, 0  |     |        | Data bus                              |  |

| 35      | RESET                       |     |        | RESET input                           |  |

| 36      | WR                          |     |        | Write input                           |  |

| 37 ~ 40 | PA7, 6, 5, 4                |     |        | Port A (BIT)                          |  |

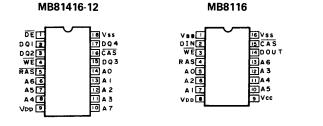

#### RAM (MB81416-12)

| Pin No. | Pin Name       | 1/0 | Active | Function                                                                                                                                |

|---------|----------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ŌĒ             | ı   |        | Output enable                                                                                                                           |

| 2, 3    | DQ1, DQ2       | 1/0 |        | Data output                                                                                                                             |

| 4       | WE             | 1   |        | Write enable, write mode at active "L"                                                                                                  |

| 5       | RAS            | 1   |        | Lower address strobe                                                                                                                    |

| 6~8     | A6, 5, 4       | 1   |        | Address input                                                                                                                           |

| 9       | VDD            |     |        | Voltage Supply +5V                                                                                                                      |

| 10~14   | A7, 3, 2, 1, 0 | I I |        | Address input                                                                                                                           |

| 15      | DQ3            | 1/0 |        | Data output                                                                                                                             |

| 16      | CAS            | 1   |        | Column address strobe                                                                                                                   |

| 17      | DQ4            | I/O |        | Data output                                                                                                                             |

| 18      | Vss            |     |        | Ground  Note) MB81416 is an N channel MOS RAM consisting of 16384 word x 4 bit. RAS only refresh type, write cycle (early write) type.; |

#### V-RAM (MB8116) (μPD416C)

| Pin No. | Pin Name    | 1/0 | Active | Function                                                                                                                                                                          |

|---------|-------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VBB         |     |        | _5V                                                                                                                                                                               |

| 2       | DIN         | 1   |        | Data input                                                                                                                                                                        |

| 3       | WE          | ı   | L      | Write enable, write mode to D-RAM at active "L"                                                                                                                                   |

| 4       | RAS         | 1   | L      | Lower address strobe                                                                                                                                                              |

| 5 ~ 7   | A0, 2, 1    | 1   |        | Address bus                                                                                                                                                                       |

| 8       | Voo         | İ   |        | +12V                                                                                                                                                                              |

| 9       | Vcc         |     |        | +5V                                                                                                                                                                               |

| 10 ~ 13 | A5, 4, 3, 6 |     |        | Address bus                                                                                                                                                                       |

| 14      | DOUT        | О   |        | Data output                                                                                                                                                                       |

| 15      | CAS         | ı   | L      | Column address strobe                                                                                                                                                             |

| 16      | Vss         |     |        | Ground                                                                                                                                                                            |

|         |             |     |        | Note) MB8116 is an M-OS-N channel RAM consisting of 16384 word x 1bit Output is three state. RAS only refresh type, write cycle (early write) type. VDD: +12V, Vcc: +5V, VBB: -5V |

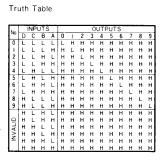

## • 74LS157 (iG059650) 2 to | Data Selectors

Truth Table

| Select Strobe G X H | OUTPUT<br>Y |

|---------------------|-------------|

| х н                 |             |

|                     | L           |

| L L                 | Α           |

| H L                 | В           |

#### **IC BLOCK DIAGRAM**

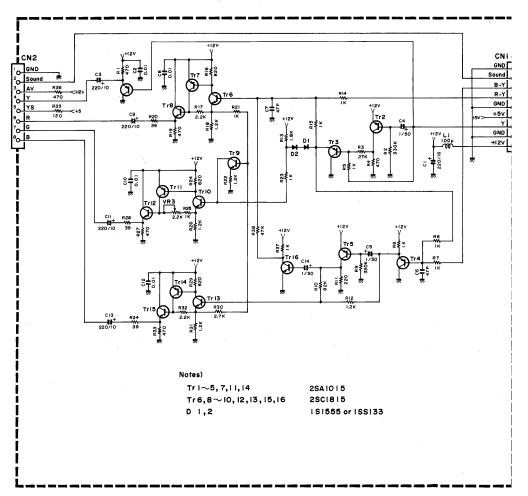

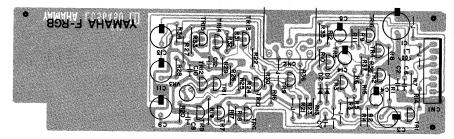

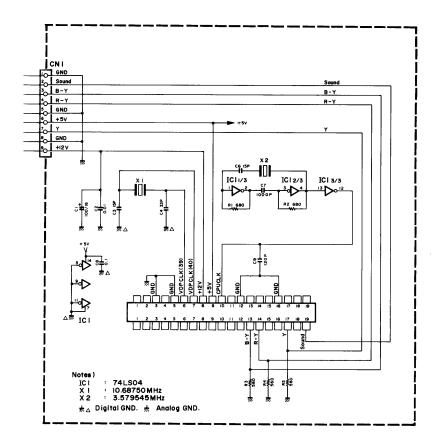

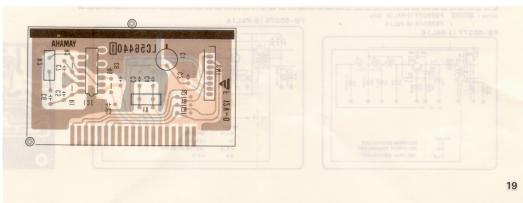

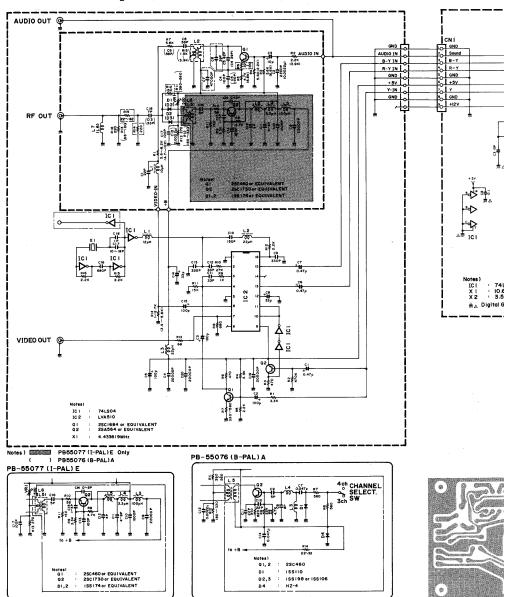

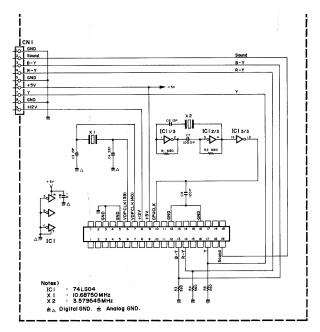

#### ● ENCODER Circuit Diagram (G-PAL) PB55075

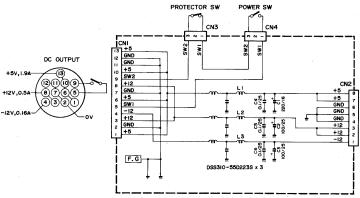

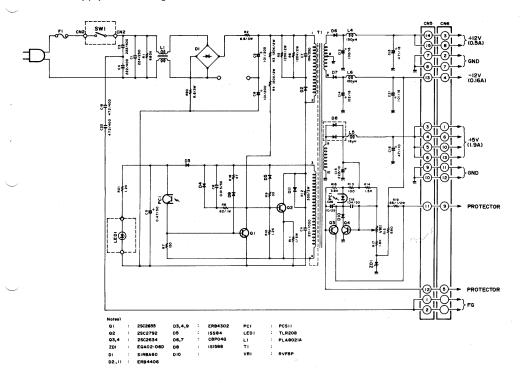

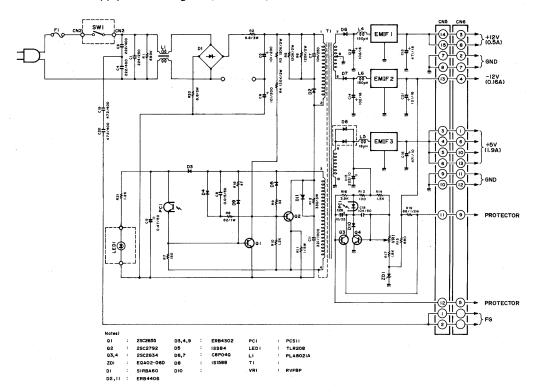

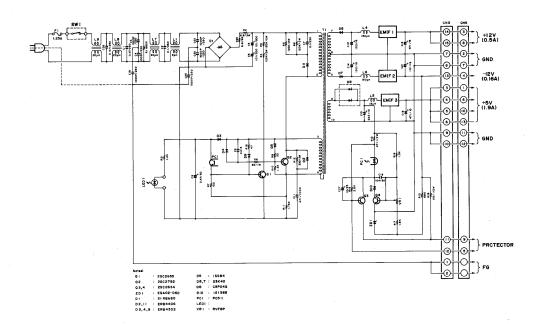

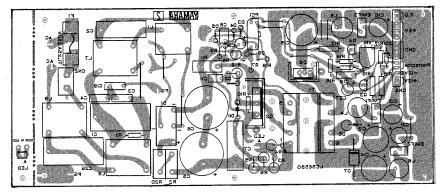

● Power Supply Circuit Diagram (NP55140, NP55150, NP55170)

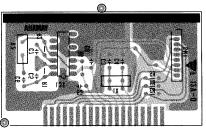

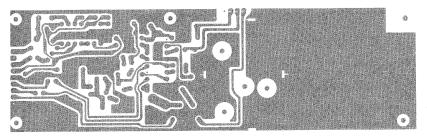

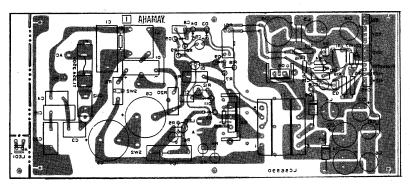

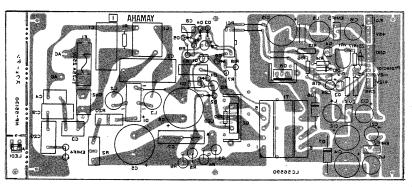

Power Supply Circuit Board

#### • Power Supply Circuit Diagram (NP55130)

#### • Power Supply Circuit Board

#### • Power Supply Circuit Diagram (NP55180)

#### ● Power Supply Circuit Board

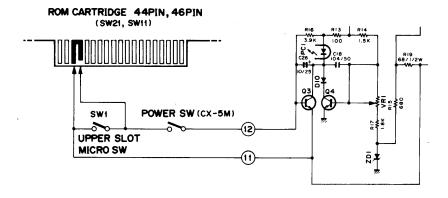

#### **■**OPERATION OF CARTRIDGE PROTECTION

The power supply circuit of this unit is the self RC circuit type and specified secondary voltageis is given by the feedback of PC-1 as shown to the figure. In the cartridge protector circuit, SW1 is shorted when the ROM cartridge is not inserted in the upper slot. For this reason, Q3 is non operating. When the cartridge is inserted, SW1 become open, Q3 is ON. In the result, the voltage supply stops. After that, when the cartridge is fully put in, Q3 becomes OFF and power is supplied because pin 44 (SW21) and pin 46 (SW11) are shorted.

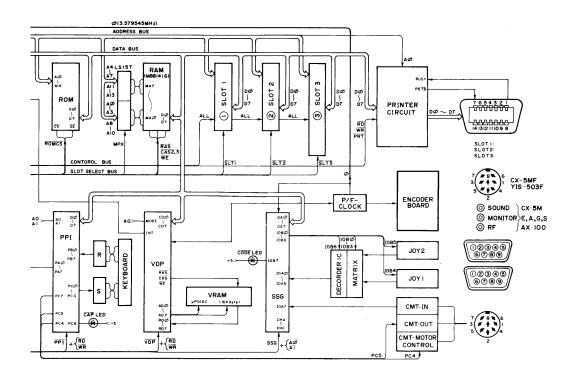

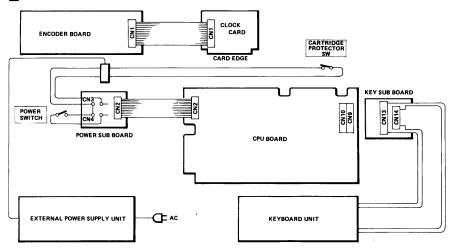

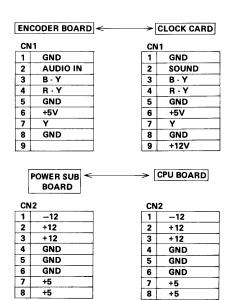

#### **WIRING BLOCK DIAGRAM**

|    | KEY SUB<br>BOARD |    | KEYBOARD<br>UNIT |

|----|------------------|----|------------------|

| N9 |                  | CN | 113              |

| 2  | ₹3               | 14 | POWER            |

| T  | ₹2               | 13 | +5               |

| T  | Y1               | 12 | X4               |

| Ī  | Ϋ́0              | 11 | X6               |

| Ī  | X7               | 10 | X1               |

| Γ  | X6               | 9  | X2               |

| Ι  | X5               | 8  | X3               |

| I  | X4               | 7  | X5               |

| Ι  | X3               | 6  | X7               |

|    | X2               | 5  | Χō               |

|    | X1               | 4  | CODE             |

|    | Χō               | 3  | +5               |

|    | GND              | 2  | CAPS             |

| 10 |                  | 1  | +5               |

| Ī  | +5               | CN | 114              |

| T  | +5               | 23 | <b>Y</b> 5       |

| Г  | +5               | 22 | ₹7               |

|    | POWER            | 21 | Υŏ               |

|    | CODE             | 20 | <b>V1</b>        |

| Γ  | CAPS             | 19 | <b>Y</b> 4       |

|    | <b>Y9</b>        | 18 | <b>Y3</b>        |

| I  | Y8               | 17 | ₹8               |

| T  | <b>Y</b> 7       | 16 | <b>Y2</b>        |

| T  | Y6               | 15 | <b>Y6</b>        |

| Ī  | Y5               |    |                  |

| Γ  | <b>Y</b> 4       |    |                  |

| _  | GND              |    |                  |

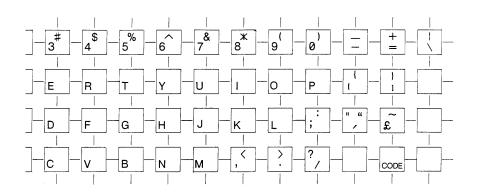

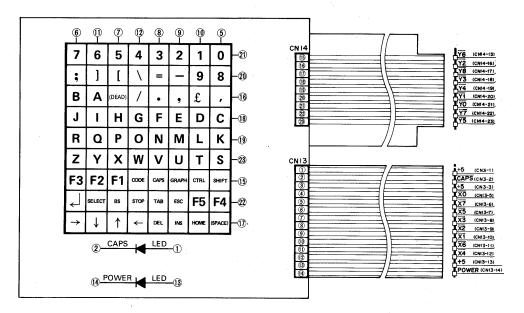

#### KEYBOARD MATRIX TABLE

Power Sub Circuit Board & Diagram

• Key Sub Circuit Board