# YAMAHA COMPUTER MSX Series

## Technical Summary

Applicable models

AX-100 Series YIS-503F Series

**CX-5M Series**

008038

Scanned and converted to PDF by HansO, 2002 Original supplied by Jetze Mellema

## **CONTENTS**

| 1. | MSX AND COMPUTER - INTRODUCTION                              | 1  |

|----|--------------------------------------------------------------|----|

| 2. | CPU BLOCK                                                    | 9  |

| 3. | MEMORY BLOCK                                                 | 27 |

| 4. | THE SLOT CONCEPT AND THE MSX MEMORY CONTROLLER (MMC, YM5214) | 43 |

| 5. | I/O PORT BLOCK                                               | 57 |

| 6. | VIDEO BLOCK                                                  | 83 |

| 7. | POWER CIRCUIT                                                | 99 |

## 1. MSX AND COMPUTER - INTRODUCTION

#### 1-1 COMPUTER

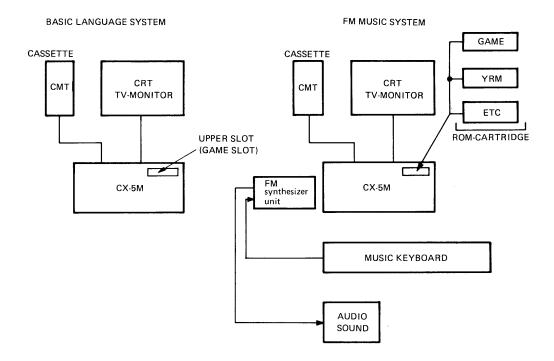

Recently, CPUs (Central Processing Units) have been incorporated into various kinds of products. In products such as musical instruments or audio equipment, which are not equipped with any keyboards (unlike microcomputers), the CPU controls the entire system. This control function and the hardware are exactly the same as those of general microcomputers. Normally, the MSX Music Computer CX-5M is a microcomputer system with the BASIC LANGUAGE programming capability. However, various kinds of units or cartridges are connected to expansion connectors, called "SLOTS", and the CX-5M can be used and enjoyed as a music system (or a musical instrument) or a game machine.

Fig. 1-1-1 MSX (CX-5M) System Diagram

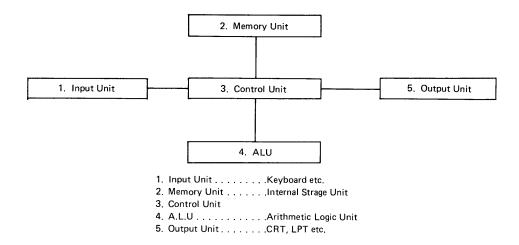

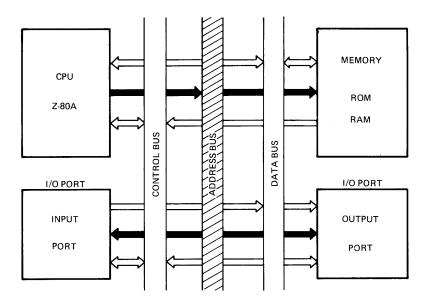

In this way, the MSX music computer CX-5M alone can play a role of various functions. Generally, in a large scale system (Main frame), the system is composed of 5 important elements of the computer, as shown in the following.

Fig. 1-1-2 5 Important Elements of Computers

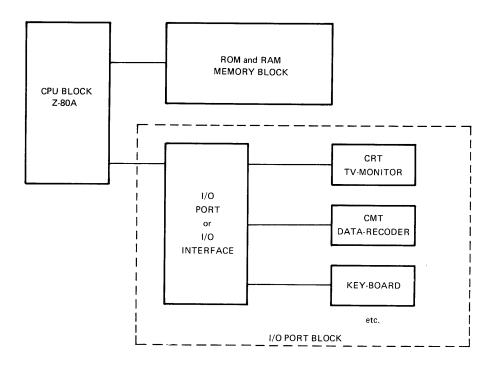

In small microcomputer systems including the CX-5M, a LSI (8-bit CPU for CX-5M) is used. It is referred to as the CPU, and it combines the Control Unit and the A.L.U in the above figure. ROMs and RAMs are used as Internal Storage Units. The Input and Output Units in the above figure are called I/O (Input/Output) Ports or I/O Interfaces, and these control the I/O of data or codes to and from external units. In this way, the block diagram of small microcomputer systems can be classified into 3 blocks, CPU, Memory and I/O port blocks.

Fig. 1-1-3 Microcomputer System Block Diagram

#### 1-2 INTRODUCTION TO CPU OPERATION

The operation of the CX-5M microcomputer seems to be very complicated. But it is nothing but the repetition of the following patterns: The CPU fetches and executes, one by one, Z-80A OP (Operation Codes) which are written in machine language and are stored in the ROM or RAM, in the exact order they have been programmed. At this time, there are only 4 basic operations of the CPU as in the following:

- 1. The Transfer of Codes and Data.

- 2. Logical Operation (AND, OR, EOR etc.)

- 3. Comparison

- 4. Programming, Jump (including IRQ processing)

The control unit within the CPU allows the CPU to execute the above 4 operations in the proper order and in the following manner.

The CPU:

- 1. Specifies the head address of the ROM or RAM (Memory Element) which has OP codes.

- 2. Reads the OP code stored at the address into the CPU.

- 3. Interprets the OP code

- 4. Following the OP code, accesses memories (ROM, RAM) and the specified addresses of I/O ports, or reads the data in the specified address into the CPU and performs arithmetic operations.

The above series of processes are always executed by the CPU of the CX-5M whatever role the CX-5M may play.

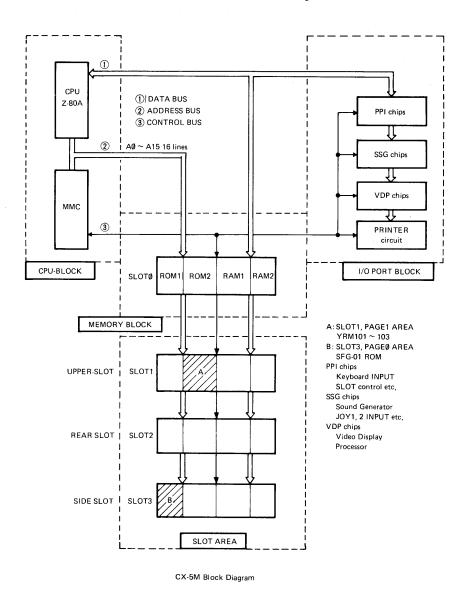

#### 1-3 CX-5M SYSTEM BLOCK DIAGRAM

The block diagram of the CX-5M system is shown as in the following.

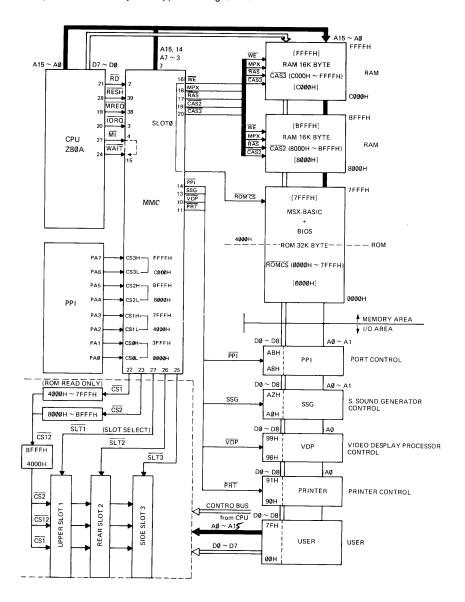

Fig. 1-3-1 CX-5M Block Diagram

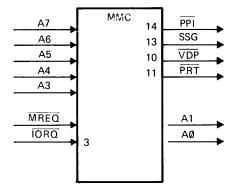

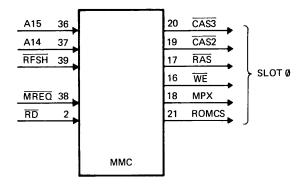

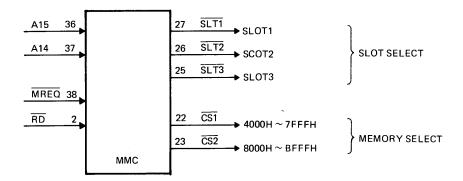

The MMC chip (40 pin LSI) of the CPU Block (Fig. 1-3-1) is custom LSI and is called the MSX-Memory Controller. It performs the following functions:

- 1. Address control of the SLOT area (the expanded memory area) which is essential to the main feature of the MSX computer.

- 2. Memory control for the entire system.

- 3. I/O port address control.

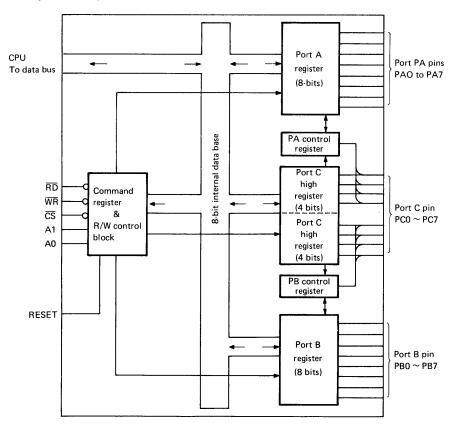

Almost all of the I/O blocks, as shown in the Fig. 1-3-1, consist of LSIs with 40 pins; especially, the LSI which is called the PPI chip which has 3 x 8 bits, parallel ports, and mainly functions as the I/O ports of the keyboard and the CX-5M SLOT control port.

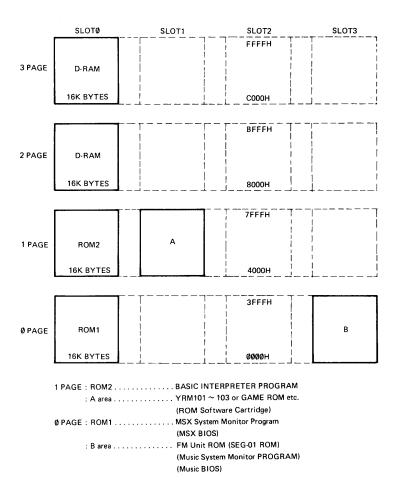

Fig1-3-2 MSX (CX-5M) Memory area

The memory block in the Fig. 1-3-2 also shows the figure on the SLOT. This is one of the best features of the MSX (CX-5M) computer. Turning on the CX-5M will automatically allow the BASIC language to be available to the user. At this time, a program BIOS (BASIC INPUT/OUTPUT SYSTEM) called the "SYSTEM MONITOR" interfaces between the hardware and the software and the BASIC INTERPRETER program is stored within the ROM of the memory block in the Fig. 1-3-2. This ROM program will permit BASIC PROGRAMMING. Then, the use of the "CALL MUSIC" command will enable the CX-5M to be used as a music system. And the SFG-01 ROM in the Fig. 1-3-2 will function instead of ROM 1. Both the Music System Monitor and the Music System Control (Music BIOS) are stored within the SFG-01 ROM. This means that these programs will commence functioning instead of ROM 1, enabling the Music System to start its operation. Next, ROMs for the YRM102, 103 and 101 shown at SLOT 1 of the Fig. 1-3-2 can be operated instead of ROM 2 within the memory block of the Fig. 1-3-2.

The BASIC INTERPRETER program occupies all of ROM 2 and can not be operated when the Music System is activated. Thus, ROMs for the YRM102, 103 and 101 are inserted into this area to allow switch over into various kinds of systems.

The following chapters deal with the hardware of the CX-5M, centering upon the 3 important blocks of the microcomputer system.

In this chapter, explanations are given regarding the CPU and its peripheral circuits which make up the central part of the Music Computer CX-5M.

## 2. CPU BLOCK

#### 2-1 CPU Peripheral Circuit Block Diagram

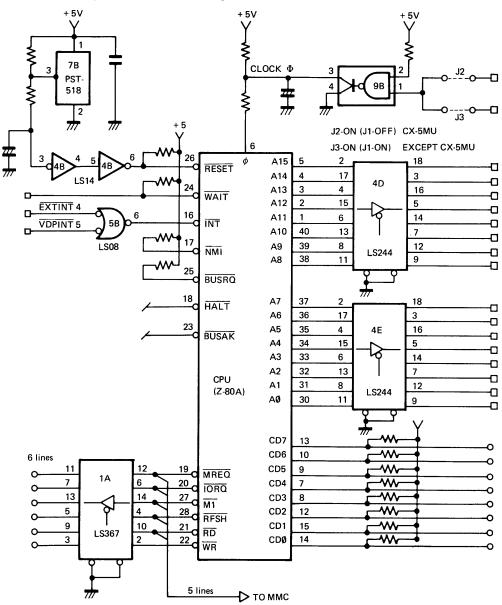

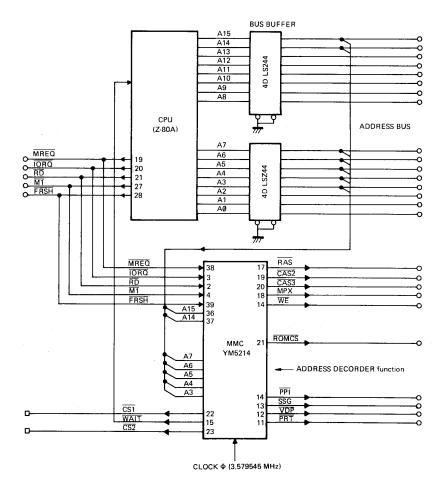

Fig2-1-1 CPU (Z-80A) BLOCK DIAGRAM

Fig. 2-1-2 ADDRESS DECODER AND MEMORY, I/O PORT BLOCK DIAGRAM

Fig. 2-1-3 CPU and MMC BLOCK DIAGRAM

#### 2-2 System Clock Circuit

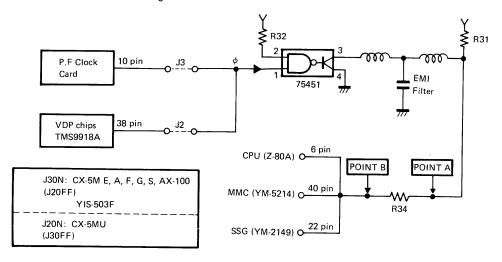

The MSX microcomputer system uses an 8 bit CPU which is equivalent to the Z-80A. The Z-80A is a high-speed version of the Z-80 and operates on system clock of 4 MHz. The system clock of the MSX computer system is 3.579545 MHz. The CX-5M computer system (hereon referred to as the CX-5M) enables this system clock to be generated by the clock card above the CPU circuit boards, and the system clock is supplied to the CPU and each LSI as shown in the Fig. 2-2-1.

Fig. 2-2-1 System Clock Supply Block Diagram

Fig. 2-2-2 Clock Timing Chart

This system clock is the reference clock for the entire operation of the CX-5M. Thus, it is crucial to check if the system clock is being supplied as it should be. By checking the waveforms of the system clock at the points A and B (Fig. 2-2-1), it can be judged if the failure occurs in the system clock generating circuit or the circuits which follow.

#### 2-3 Z-80A CPU Control Bus Lines

As described in the preceding sections, the Z-80A is used as a CPU in the CX-5M. For operating this CPU, various kinds of lines are connected to it. In this section, explanations are given on various control lines called the "control bus," which are used for determining whether the CPU is functioning normally, or if it is in halt. If the CPU is in halt, it also must be determined if the CPU is in halt because of its breakdown or external failure.

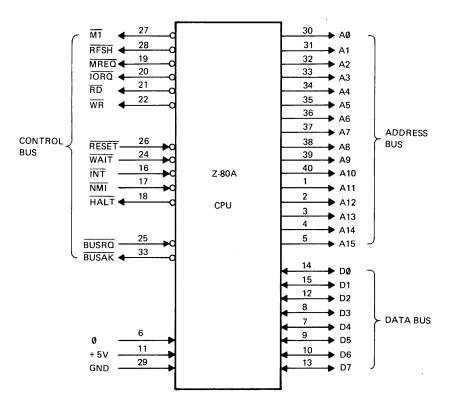

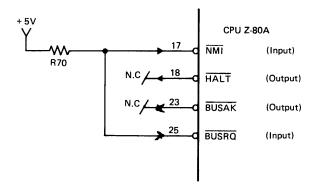

Fig. 2-3-1 Z-80A Pin Assignments

As shown in the above Fig. 2-3-1, the 40 pins of the Z-80A can be classified into 3 groups and the Z-80A is equipped with a total of 13 control lines. In the MSX Computer System, the following 4 out of the above 13 control lines are not in use. These unused pins are treated in the following manner on the circuit board of the CX-5M CPU.

1.  $\overline{\text{NMI}}$  (pin 17) Non-maskable Interrupt Request Input. This pin is pulled up to +5V.

2. HALT (pin 18) Halt. This output shows that the CPU is in halt. This pin is unconnected.

BUSAK (pin 23) Bus Acknowledge Output. This is used for DMA (Direct Memory Access) transfer. This pin is unconnected.

4. BUSRQ (pin 25) Bus Request Input. This is used for DMA transfer. This pin is pulled up to +5V.

Fig. 2-3-2

As shown in the above, Non-Maskable Interrupt Request and data transfer by DMA are not supported by the CX-5M.

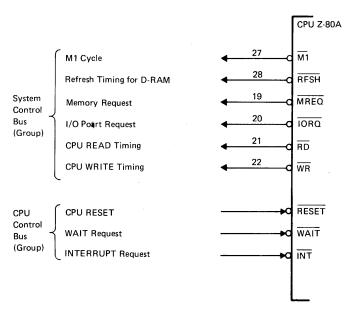

#### 2-4 CONTROL BUS

In the CX-5M, the CPU (Z-80A) transmits control information through 9 control lines. These 9 control lines can also be classified into the CPU Control Group and the System Control Group.

Fig. 2-4-1 CPU Z-80A Control Bus Terminal

#### 2-4-1 System Control Bus Group

The System Control Bus Group is used for outputting control signals (of either high or low logic level) from the CPU to external devices including ROMs. RAMs, and I/O ports.

#### M1 (pin 27) < OUTPUT >

The M1 signal is sent out from the CPU to show that the CPU is currently reading (or fetching) an OP (Operation) code from the internal memory devices including ROMs or RAMs into the CPU.

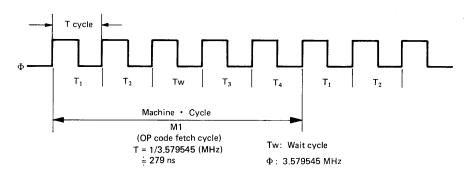

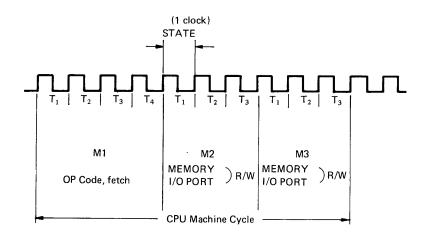

Fig. 2-4-2 CPU Basic Timing (Machine Cycle) Chart

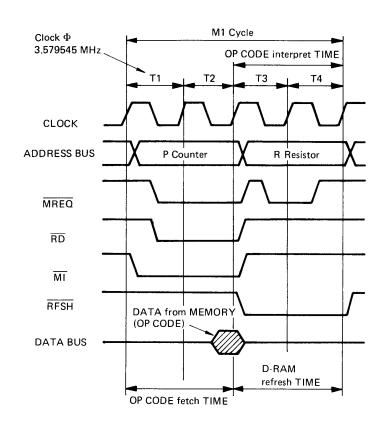

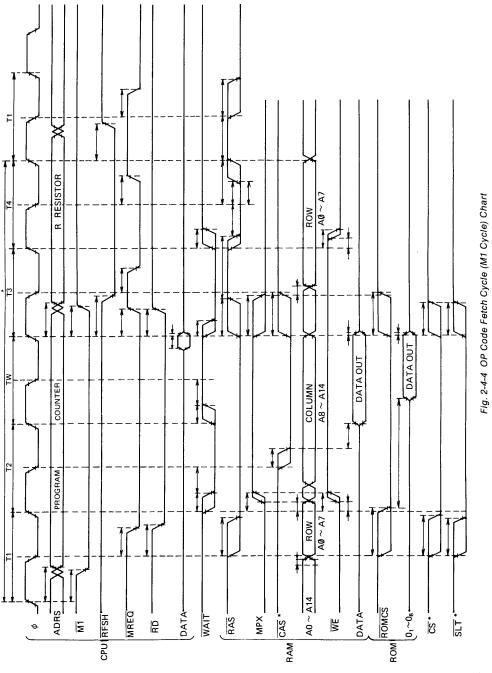

Fig. 2-4-3 OP Code Fetch Cycle (M1 Cycle) Chart

**–** 16 –

#### Note: Machine Cycle (M)

The following are the basic operation patterns used when the CPU executes programs. The repetition of the basic operation patterns will allow all programs (written by machine language) to be executed. The basic operation patterns are:

- 1. Fetching (Reading) Operation for OP codes.

- 2. Interpretation of OP codes.

- 3. READ/WRITE Operation of Memory Areas.

- 4. READ/WRITE Operation of I/O Ports.

- 5. Internal Operation of CPU.

- 6. IRQ (Interrupt Request) Process.

Normally, the basic operation patterns consist of a combination of the above 6 patterns. However, any basic operation pattern will start with both pattern 1 and 2. The combination of the above patterns 1 and 2 is called the "M1 cycle." And the combination of patterns from 3 to 4 is called the "M (Machine) cycle" and it is different from the M1 cycle. The M1 cycle is available for executing the following operations which can not be realized in other machine cycles.

- 1. Interpretation of OP Codes.

- 2. DRAM (Dynamic RAM) Refresh Control (See Fig. 2-4-3)

Note that the DRAM refresh control can be executed only in the M1 cycle. Now, let's take a look at the machine cycles, using machine language programs.

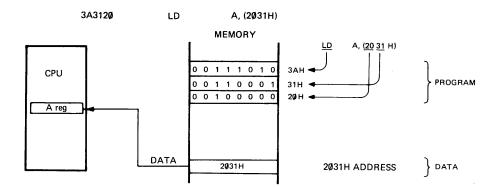

Fig. 2-4-5 LD A, (2031H) Program Sample

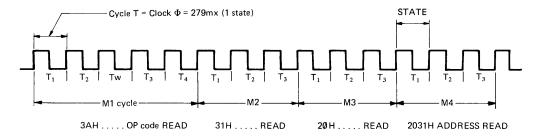

The program given in Fig. 2-4-6 allows data stored in the address 2031H (H = Hexadecimal) to be read and stored into the register A within the CPU. The following shows the machine cycle in that the CPU executes this OP code.

Fig. 2-4-6 Machine Cycle for OP Code LD A, (2031H)

- 1. The CPU will fetch the OP code (3AH) during the machine cycle M1.

- The OP code fetched in M1 is interpreted within the CPU, when the external dynamic RAM chips are refreshed.

- 3. The data necessary for the OP code interpreted in the machine cycle M1 is read in the machine cycles M2 and M3. The address data "20H" and "31H" stored in the memory after the OP code is read into the CPU and is set at the address counter within the CPU.

- 4. The CPU outputs the address data "2031H" to the address bus in the machine cycle M4. The data stored in the address "2031H" is read into the internal register A within the CPU. The CPU Z-80A thus performs these machine cycles and keeps executing machine language programs. The above example consists of 4 machine cycles but generally the machine cycle varies from 1 to 6 depending on each command. Also, each machine cycle is composed of several states. Each state has the same length: one T period of the system clock Fig. 2-4-6. Namely, the M1 output of the CPU system control buss is the signal outputted from the CPU while the CPU is executing the M1 machine cycle, and this output is called the M1 output signal during the instruction fetch cycle. The CPU announces that the CPU is executing the OP code fetching operation by outputting the M1 signal.

Since the M1 signal shows that the CPU is currently executing an OP code fetching operation, a checking signal on pin 27 makes it possible to know if the CPU is functioning normally.

The M2 can also be outputted on the following occasion: when there is an interrupt from an external device to the CPU and the CPU accepts this interrupt signal, the CPU makes both the M1 and IORQ signals to be low (0V) to fetch OP codes or address vectors into the CPU from the external device which requested an interrupt to the CPU.

#### MREQ (pin 19) and IORQ (pin 20) < OUTPUT >

MREQ indicates that this cycle involves a READ/WRITE operation of memory while IORQ identifies an input cycle from an external I/O device. These two will not go low simultaneously.

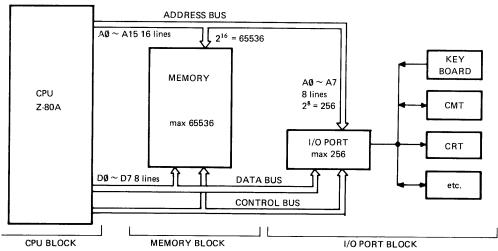

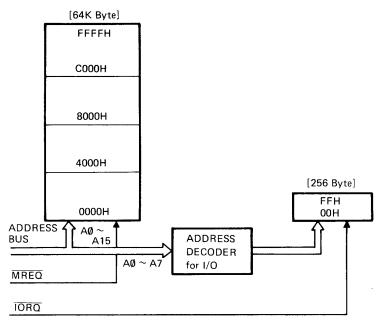

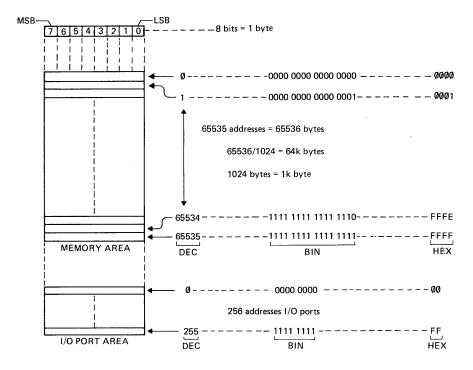

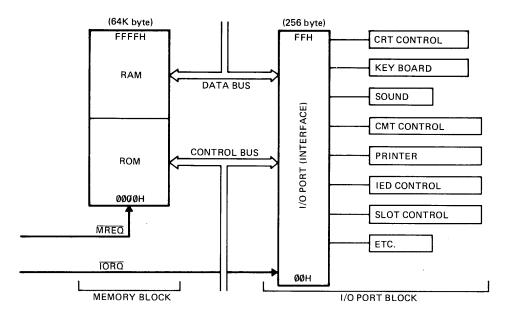

① CPU (Z-80A) MEMORY and I/O PORT MAP DIAGRAM

② CX-5M I/O PORT DECODER by MMC chip

Fig. 2-4-7 CPU (Z-80A) Memory and I/O Area Block Diagram

As shown in Fig. 2-4-7, the CPU is provided with two areas: The Memory Area (0000H  $\sim$  FFFFH = 65536 Bytes = 64 Kbytes) I/O Area (00H  $\sim$  FFH = 256 Bytes)

Address lines A0  $\sim$  A8 are connected to both the memory and I/O areas (address lines A9  $\sim$  A15 are also connected to the memory area). Thus, if the CPU sends address data, 00H  $\sim$  FFH, to the lowermost 8 bits (A<sub>0</sub>  $\sim$  A<sub>7</sub>), both of the memory and I/O areas are selected simultaneously. To prevent this, the MREQ goes low (0V) for selecting memory areas or the IORQ goes low (0V) for selecting I/O areas.

In the MSX-BASIC language, POKE and PEEK commands are available for accessing memory areas and IN and OUT commands for I/O areas.

**- 20 -**

Fig. 2-4-9 Timing Chart for Accessing I/O Areas

The MREQ signal, along with the RFSH signal (pin 28), goes low (0V) for refreshing the dynamic RAMs. The IORQ signal, along with the M1 signal, is also used for responding to an interrupt request\*\*\*

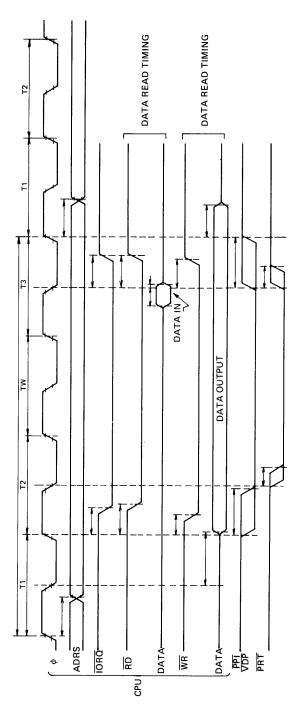

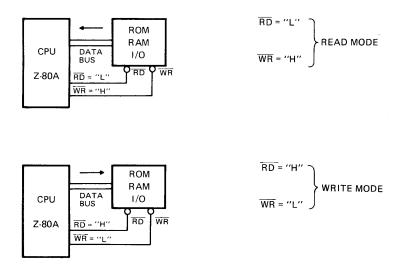

#### RD (pin 21) and WR (pin 22) < OUTPUT >

There are CPU commands regarding data transfer. There are two types of data transfer: data transfer from the CPU to external devices (memory and I/O areas) and from external devices to the CPU.

- Data transfer from the CPU to external devices:

WRITE Operation

- 2. Data transfer from external devices to the CPU: READ Operation

On this occasion, the data is transferred in parallel via 8 data busses. The RD and WR system control busses determine if the CPU is attempting to perform READ operation or WRITE operation with the external devices that the CPU accesses.

Fig. 2-4-10 Read/Write Mode Operation

As shown in Fig. 2-4-10, the direction of the data movement within the 8 data busses (for 8 bits) for the READ operation is opposite to that of the WRITE operation. These READ and WRITE signals are used for controlling the direction of the bidirectional buffers for busses.

#### RFSH (pin 28) < OUTPUT >

Dynamic RAMs are used as main memories of the CX-5M. Without the refresh operation, these dynamic RAMS would lose data stored inside. The RFSH is an output signal from the CPU (Z-80A) for refreshing the dynamic RAMSs. The RFSH signal is outputted only in T3 and T4 states (OP code interpretation) of the M1 cycle (OP code fetch cycle) which was described before. And only at this time, can the dynamic RAMs be refreshed (Fig. 2-4-3).

The Row Address of the dynamic RAM, which is counted by the memory refresh register "R" within the CPU, appears on the address busses in Fig. 2-4-3. The address for performing refreshing is set by this operation. The RFSH signal goes low (0V) at the timing shown by Fig. 2-4-3 for performing refresh of the dynamic RAMs.

As shown in Fig. 2-4-3, the MREQ signal also goes low (0V) to show that the CPU is attempting to refresh memory areas. For maintenance purposes, observe the RFSH (pin 28) signal on the synchroscope to ensure that the CPU is outputting the refresh signal for dynamic RAMs. The operation of the CPU can also be checked simultaneously.

#### 2-4-2 CPU Control Buss Group (RESET, WAIT, INT)

The CPU control busses are used for externally controlling the CPU operation. Thus, these busses are essential for checking the operation of CPU.

The signals other than the RESET signal are input signals to the CPU. These signals go low at certain a fixed timing for telling the CPU to perform WAIT or INTERRUPT operation. When faults result in circuits other than the CPU and either of these CPU control busses goes low (0V) accidentally, the operation of the CPU will not be guaranteed. Especially, when the RESET signal is being held low (0V), the CPU will not function at all. Also, holding the WAIT signal low (0V) will disable the refreshing of the dynamic RAMs and hence result in faulty data within the dynamic RAMs. In this situation, the execution of programs is not possible.

#### RESET (pin 26) < INPUT >

In the CX-5M, the RESET operation is performed automatically when the power is turned on. At this time, each device including LSIs can be reset.

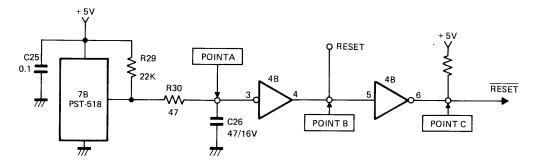

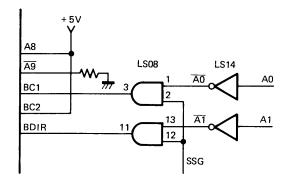

Fig. 2-4-11 Reset Circuit for CX-5M

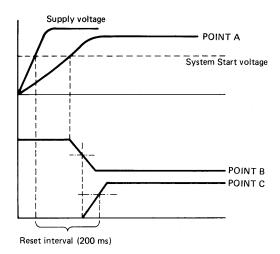

When the power is turned on, the signal on pin 3 of the PST-518 reaches a constant voltage in a short time. But, the voltage at point A increases gradually depending on the time constant determined by R30 and C26. The time required for this signal to reach the threshold voltage level of the TTL 74LS14 is the reset time when the power is turned on.

The reset time is approximately 200 mS in the CX-5M.

Fig. 2-4-12 Reset Timing Chart

During the reset operation, the following operations occur within the CPU:

- 1. Interrupt is disabled.

- 2. Program counter, I register, and R register are all cleared.

- 3. Interrupt mode is set to 0.

Namely, initial conditions are set within the CPU. Also, as shown in Fig. 2-4-11, the RESET signal is fed to other devices to reset them. Note that only PPI (LSI) can be reset by Hight (+5V) signal. When the MMC (LSI) is reset, the ROMCS signal of SLOT 0 always appears due to internal operation. When the RESET signal of the CPU is held low, the CPU will not function at all.

#### WAIT (pin 24) < INPUT>

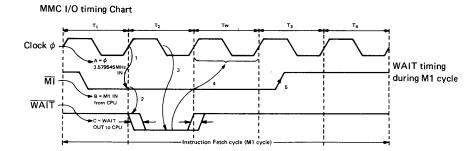

The WAIT signal is used for requesting the CPU (Z-80A) to delay operation timing. When this signal goes low (0V), the CPU inserts Tw, one period of clock  $\Phi$ , within the machine cycle when this WAIT signal is received. During the period Tw, the CPU holds the status at the time the WAIT signal is received without executing the next operations.

- A: "L" of M1 during Instruction Fetch cycle 1 and 2 is fetched at the rise time and WAIT is made low.

- B: WAIT ("L") is sent to the CPU. The CPU fetches this signal at the fall time, Wait time Tw is inserted.

- C: Internally returned to "H".

Fig. 2-4-13 WAIT Timing Chart for CX-5M

For example, when the CPU attempts to access to external devices (ROMs, RAMs, I/O ports etc.) at a slow operation speed and needs to synchronize with their speed, the CPU inserts the WAIT timing Tw by setting the WAIT signal low (0V).

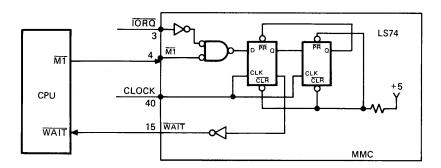

Since it is prescribed in the MSX specification that one WAIT be inserted in the M1 cycle, the CX-5M allows the WAIT signal to be fed to the CPU.

Fig. 2-4-14 WAIT Signal Generation Circuit

The WAIT signal in Fig. 2-4-13 is used for securing time for reading programs or data from ROMs which are slow in access time and is used for SLOTs 1-3 (described later in this manual).

In the CX-5M, the M1 signal which always appears at the instruction fetch cycle (M1 cycle) is fed to the MMC (LSI) where a timing is made as shown in Fig. 2-4-14. The timing made within the MMC is fed to the WAIT (pin 26) again.

When the WAIT signal is kept at low (0V), the Tw clock is continuously inserted. This leads to loss of data which was stored in the dynamic RAMs because the CPU can no longer refresh the dynamic RAMS. Thus, observing the WAIT signal is exceedingly important for checking the operation of the CPU.

#### 2-4-3 Checking CPU Operation

The summary on the pins of the CPU is given in the following:

| Source voltage   | + 5V and ± 12V for V-RAM  When the CPU fetches an instruction, an "L" pulse is always transmitted.  When the CPU fetches an instruction, an "L" pulse is always issued.  "L" pulse input of the almost same timing as that of M1.  When this pin is at low level, the CPU enters in the wait state. |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Block φ          |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CPU27 pin (M1)   |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CPU24 pin (WAIT) |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CPU28 pin (RFSH) | Refresh pulse for main D-RAM                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CPU16 pin (INT)  | "L" pulse input of 1/60 sec cycle (in the MSX-BASIC mode) "H" ouput in the MSX-BASIC mode No slot is selected,                                                                                                                                                                                      |  |  |  |  |  |

| MMC25, 27 pin    |                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| MMC28 ∼ 35 pin   | "L" output (all pins) in the MSX BASIC mode (Slot 0, MSX-BASIC Select)                                                                                                                                                                                                                              |  |  |  |  |  |

| MMC17 ~ 20 pin   | RAS, CAS2, CAS3, and MPX control outputs for main D-RAM.                                                                                                                                                                                                                                            |  |  |  |  |  |

<sup>\*</sup> MPX . . . . RAS, CAS2, and CAS3 timing switch signal

Fig. 2-4-15 CPU Check Points

Careful observation of the signal on each pin will allow you to determine to some extent if the CPU itself is faulty or the circuits other than the CPU are faulty. In this regard, the checkpoints shown in the Table 2-4-15 are extremely essential.

#### Side Slot (SLOT 3) Connector

The FM Sound Synthesizer Units are incorporated in the side slots of the CX-5M. The connector in use is a 60-pin edge connector and the assignment of pins 11  $\sim$  60 is the same as that for the upper slot (SLOT 1).

<sup>\*</sup> When an error occurs, check the above points mainly to find out the error point.

### 3. MEMORY BLOCK

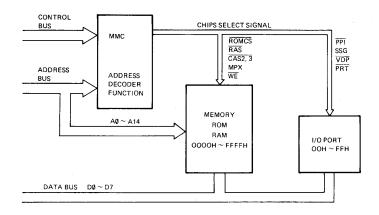

This section describes the CPU of the CX-5M microcomputer system and also the system memory map. A block diagram of the memory area appears in Fig. 3-1-1.

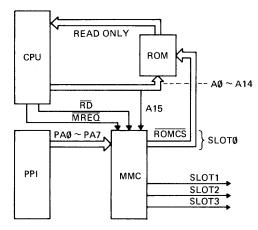

Fig. 3-1-1 Block Diagram of the CPU, MMC, ROM, and RAM, and I/O

#### 3-1 CPU (Z-80A) and reset operation

As you turn on power to the CX-5M system, the reset circuit becomes active and causes the reset pins on the CPU and the MMC to go low (OV), thus resetting them.

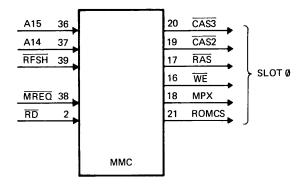

Immediately after the CPU is reset, all 16 bits of the address bus A0  $\sim$  A15 go low (OV). In the system now, read operation may start with address 0000H in the memory area. This requires that the MSX-BASIC-ROM be mapped on the memory area with 0000H as the starting address. The MSX-BASIC-ROM (32K bytes comprising 62768 addresses) corresponds to addresses 0000H to 7FFFF in the memory area. When the CPU reads from this area, it must select the area correctly. For this purpose, the ROMCS signal is provided; it is issued by the YM5214 (MMC) which operates as an address decoder. In addition, this IC decodes and issues the select signals for slots 0  $\sim$  3 (Fig. 3-1-1). Immediately, the CX-5M is reset with power-on, the CPU reads the contents of address 0000H in the slot 0 memory area in ROM (Fig. 3-1-1), that is, the MSX-BASIC-ROM. The slot select signal from the MMC must be set now to select the slot 0 memory area.

For this reason, at power-on-reset, the RESET signal is supplied to the MMC chip to allow selection of the slot 0 memory area. Following this, the program can select other slots.

#### 3-2 CPU (Z-80A) memory area and CX-5M memory map

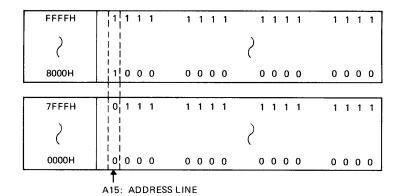

The following is a description of the CPU (Z-80A) memory area and the CX-5M memory map.

The 8-bit CPU (Z-80A) used in the CX-5M has a 16-line address bus and an 8-line data bus. The 16 address lines make it possible to select memory elements corresponding to 2<sup>16</sup> addresses (65536 addresses). Each memory element may be conceptualized as a box that may store eight segments (8 bits), each corresponding to the 'L' or 'H' states.

Fig. 3-2-1 Z-80A (CPU) memory area

In the CX-5M system, the 64K byte memory space is controlled by splitting it up into four 16K byte blocks. The memory may be extended by a 16K-byte block at a time. To select a 16K-byte block, you need bits A14 and A15 of the address line.

As the figure shows (Fig 3-2-2), fourteen addresses lines A0  $\sim$  A13 allow you to specify any one of the 16384 addresses in any one of the four blocks. However, the 14 addresses lines alone do not make it possible for the system to ascertain which block (0page  $\sim$  3page) you are selecting the address from. To ascertain this, the system must decode the two bits A14 and A15. This makes it possible to select any one of the addresses in the 64K byte (65536) space. (Fig. 3-2-2).

|       |                           |       | $A\emptyset \sim A13 = 14 \text{ lines } (16384 \text{ bytes})$ |     |            |                 |

|-------|---------------------------|-------|-----------------------------------------------------------------|-----|------------|-----------------|

| A15   | AQ                        | )     | A15                                                             | A14 | AØ ~ A13 - | 16384 addresses |

| 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 | FFFFH |                                                                 |     |            |                 |

|       |                           |       |                                                                 |     |            |                 |

| 1 1   | 16K-byte 3 page           |       | 1                                                               | 1   | RAM3       | 16384 bytes     |

|       |                           |       |                                                                 |     |            |                 |

|       | 00000000000000            |       |                                                                 |     |            |                 |

| 1 0 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 | BFFFH |                                                                 |     |            |                 |

|       |                           |       |                                                                 |     |            |                 |

| 1 0   | 16K-byte 2 page           |       | 1                                                               | ø   | RAM2       | 16384 bytes     |

|       |                           |       |                                                                 |     |            |                 |

|       | 0000000000000             |       |                                                                 |     |            |                 |

| 0 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1   | 7FFFH |                                                                 |     |            |                 |

|       |                           |       |                                                                 |     |            |                 |

| 0 1   | 16K-byte 1 page           |       | 0                                                               | 1   | ROM        | 16384 bytes     |

|       |                           |       |                                                                 |     |            |                 |

|       | 0000000000000             |       |                                                                 |     |            |                 |

| 0 0 1 | 111111111111111111        | 3FFFH |                                                                 |     |            |                 |

|       |                           |       |                                                                 |     |            |                 |

| 0 0   | 16K-byte Ø page           |       | 0                                                               | 0   | ROM        | 16384 bytes     |

|       |                           |       |                                                                 |     |            |                 |

| 000   | 0000000000000             | 0000Н |                                                                 |     |            |                 |

CX-5M Internal memory area (SLOTØ)

Fig. 3-2-2 CX-5M System memory area

Suppose that the CPU designates address A500H on the address bus. If 'A' in hexadecimal is converted into binary, we get AH = 10 = 1010B. The bit pattern is  $A^{15}$  (101001010000)  $A^{0}$ . Since bit  $A^{15} = 1$  and bit  $A^{14} = 0$ , the address is selected from block 2 page (RAM 2) (Fig. 3-2-2).

To decode the two most significant bits A15 and A14 and select the memory device in the areas 0, 1, 2, and 3page, the CX-5M decodes and issues the corresponding chip select signal by means of the MMC chips.

#### 3-3 CX-5M MSX-BASIC-ROM and RAM area

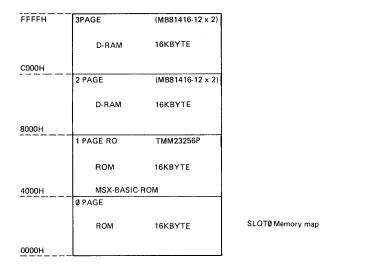

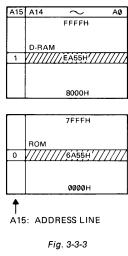

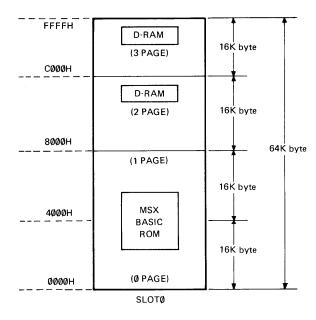

The 64K byte memory area in the CX-5M is referred to as slot 0. The memory map of this area appears in Fig. 3-3-1.

ROM stores the following programs, MSX-BASIC being activated as the power to CX-5M is turned on.

- 1. MSX-OS system monitor (program controlling the entire CX-5M)

- 2. MSX-BASIX Interpreter (runs the MSX-OS and the BASIC program)

MSX-OS is referred to in general as the monitor program. It provides an interface between the external I/O units (TV, CRT, keyboard, CMT, etc.) and the CPU. Furthermore, it controls the entire CX-5M system. In this way, it is a program performing very important operations. As for the MSX-BASIC interpreter, it compiles the user coded BASIC programs into the machine language program that the CPU can understand. Again, MSX-OS may be considered as a group of subroutines written in the machine language. For a user running a monitor subroutine, a uniform access method is offered for the part of the programs called MSX-BIOS. This assures compatibility among the software products.

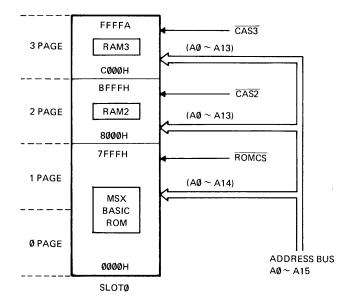

Let us now see the hardware feature related to the mapping of the ROM and D-RAM into the memory space and access to the ROM and D-RAM.

Fig. 3-3-1 Slot 0 Memory Area

#### 3-3-1 ROM area (MSX-BASIC ROM 0000H ~ 7FFFF 32K byte)

In the MSX ROM, chips are selected by setting CS and OE low. As Fig. 3-3-1 shows, signal ROMCS is entered in the ROM.

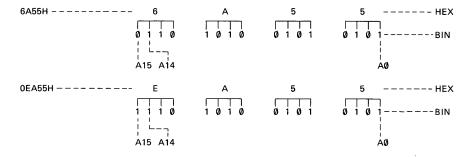

Let us imagine that the CPU has issued address data to select 6A55H and EA55H on the address bus.

Fig. 3-3-2

The MSX-BASIC-ROM is provided with fifteen address lines input pins (A0  $\sim$  A14), making it possible to select 215 (= 32768; 32768: 1024 = 32K bytes) memory areas.

As in the above example, if the CPU selects addresses 6A55H or EA55H, address 6A55H alone will be selected addresses 6A55H alone willin either instance within the ROM because address lines A15 are not connected within ROM. In order to avoid this, address A15 is used as dip select signal.

In other words, as Fig. 3-3-3 shows, the ROM may be selected according to the state (high or low) of A15. This,

Fig. 3-3-4

Since A15 is low("0") in the interval 0000H and 7FFFF and high ("1") in the interval 8000H and FFFFH, input of A15 in ROMCS makes it possible to select one of the addresses in the 64K byte space. Have a look at the block diagram of the MXS memory are (Fig. 3-3-1). You will notice here that ROMCS entering MSX-BASIC-ROM is not from address line A15 but from ROMCS of MMC. This is because the following conditions apply simultaneously when the CPU selects MSX-BASIC ROM:

- 1. Slot 0 is selected

- 2. An access to the memory

- 3. ROM contents are valid only in the Read mode (when the data and the program are read).

In the above conditions, the program running at the time causes input of the following control signals from the CPU to MMC:

- 1. 8-bit signal from PPI port A to select slot 0 (see later)

- 2. Control bus MREQ goes low when the CPU selects a memory area.

- 3. RD is low when the CPU is in the Read mode. These control signals and the state of address line A15 are entered in the MMC where these are decoded. These may be issued from the ROMCS pin of the MMC if the prevailing conditions permit.

Fig. 3-3-5

#### 3-3-2 RAM AREA

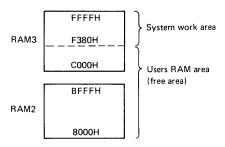

Capacity of the memory area available to the user is indicated at Left top of the screen as soon as the CX-5M is connected to power and MSX-BASIC is activated. The data appearing here will show that the space available is smaller than 32K bytes. This is because the area available is a temporary one, forming part of RAM, being given to the user when the CPU (Z-80A) is on. This particular RAM area is referred to as the system work area, occurring from F380H to FFFFH in the CX-5M. If you use BASIC, you need not concern yourself about this area.

Fig. 3-3-6 Block Diagram of the RAM Area

Read/write operations in the RAM area of CPU does not differ basically from ROM read operations.

In the CX-5M, the RAM used is a D-RAM. For this reason the read/write operation here calls for the following:

- 1. Periodic refreshing

- 2. Provision of addresses and data in two rounds (instead of one)

- 3. There are read and write modes for these operations.

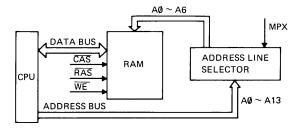

Fig. 3-3-7 RAM Peripheral Circuit

As explained earlier, the ROM (MSX-BASIC-ROM) used is a 32K byte maskROM. It occurs in the memory from 0000H to 7FFFH. As for the RAM, it consists of two 16K byte blocks, adding up to a 32K byte area. It is assigned the memory area extending from 8000H to FFFFH.

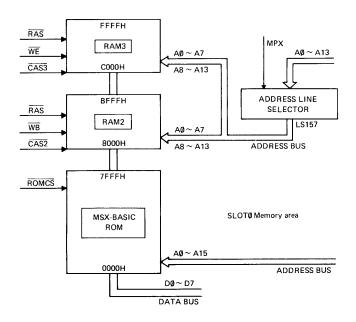

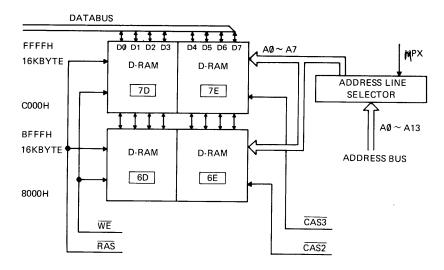

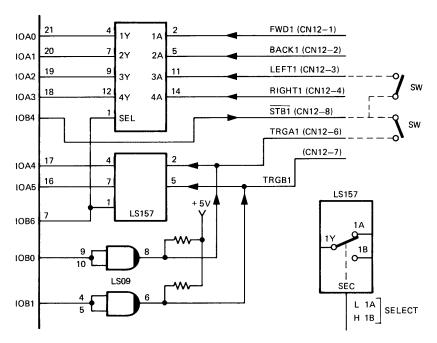

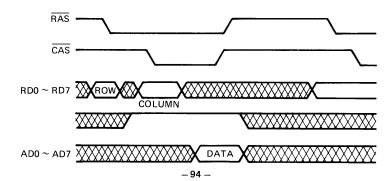

Fig. 3-3-8 D-RAM Memory Block Diagram

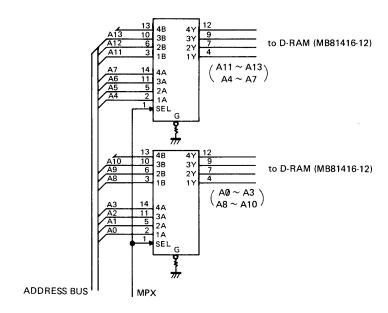

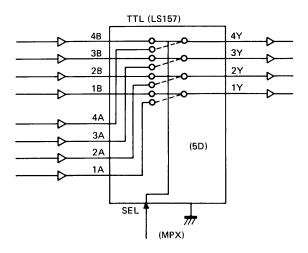

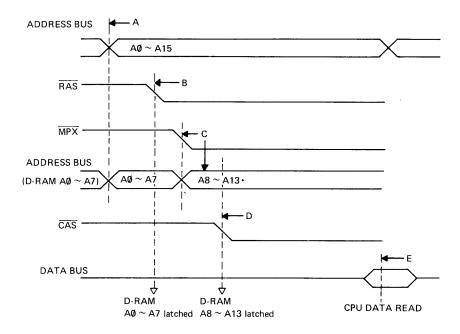

Have a look at the D-RAM (Fig. 3-3-§). First take the point depending on whether the signal entering the SEL pin is low or high, either the group-A pins (1A  $\sim$  4A) or the group-B pins (1B  $\sim$  4B) are led to output pins 1Y  $\sim$  4Y. At the SEL pin, input of the MPX signal takes place from the MMCLSI chips. Accordingly, address and data are switched between A0  $\sim$  A7 and A8  $\sim$  A13 To the address bus selector, 14 address lines (A0  $\sim$  A13) are connected. This indicates that a memory space of 2<sup>14</sup> or 16384 bytes, that is 16K bytes, can be selected within D-RAM by using address lines A0  $\sim$  A13. However, only eight address inputs (A0  $\sim$  A7) are possible for D-RAM as the terminals show. This is because D-RAM receives the address data at two timings: RAS timing and CAS timing. The address data is divided into two timing schemes by the TTL chips (74LS157) in the address line selector.

Fig. 3-3-9 Address Line Selector

Let us now turn to the operations of the TTL chips.

Fig. 3-3-10 TTL 74LS157 Internal Block

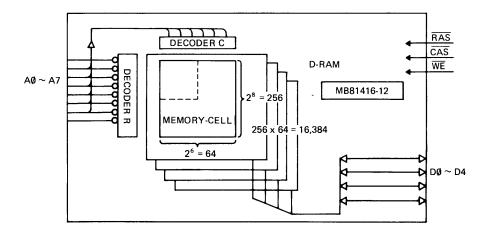

Next have a look at the internal block diagram for the D-RAM chips (MB81416-12).

Fig. 3-3-11 MB81416-12 Internal Block

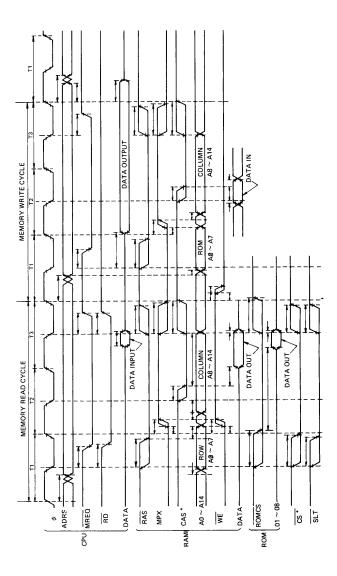

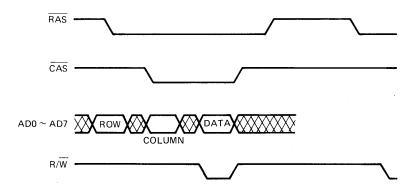

The following explains the D-RAM chip operations with reference to the timing chart. (CPU READ MODE)

- 1. The CPU (Z-80A) issues addresses data (A0  $\sim$  A15) to the address bus (A in Fig. 3-3-12).

- 2. At the trailing edge of the RAS signal from the MMC chip (B in Fig. 3-3-12), the contents of address A0 ~ A7 are latched in decoder R (Fig. 3-3-11).

- 3. From MMC clip, the MPX signal is sent to the TTL chips (74LS157), and address A8  $\sim$  A13 will appear at address pins A0  $\sim$  A7 of the D-RAM (C in Fig. 3-3-12).

- When CAS enters D-RAM from the MMC chips the contents of address A8 ∼ A13 are latched in decoder C (Fig. 3-3-11), (D in Fig. 3-3-12).

- When CAS is entered in the D-RAM chip, data stored in the memory cell is output to data output pins D0 to D4. (Ein Fig. 3-3-12)

Fig. 3-3-12 D-RAM Timing Chart

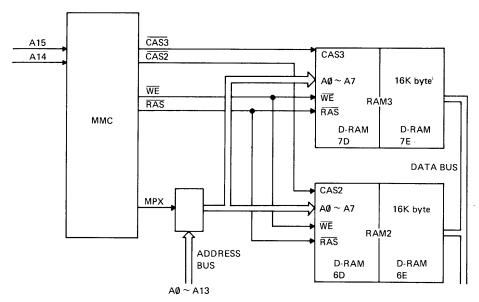

As Fig. 3-3-11 shows, the D-RAM chips (MB81416-12) process 4 bits of data simultaneously. For this reason, the D-RAM chips are paired into two or four, respectively, an 8-bit, 16K-byte memory configuration (Fig. 3-3-8).

The D-RAM pairs are used to form a 32K byte memory in the CX-5M.

Next, we will take up address decoding for the D-RAM chips.

As we have already seen, the internal addresses in the D-RAM chips are selected by means of 14 address lines A0  $\sim$  A13. However, these 14 address lines cannot determine where in the 64K byte memory (from 0000H to FFFFH) the respective 16-K byte memories can be allotted. The two address lines A14 and A15 are required to determine this.

Fig. 3-3-13 MMC circuit diagram of the memory (D-RAM)

| A15 | A14 | Α1 | 3 |   |   |   |    | $\overline{}$ | _ |   |   |   |   |   | AØ | ADDRESS |              |

|-----|-----|----|---|---|---|---|----|---------------|---|---|---|---|---|---|----|---------|--------------|

| 1   | 1   | 1  | 1 | 1 | 1 | 1 | 1  | 1             | 1 | 1 | 1 | 1 | 1 | 1 | 1  | FFFF    |              |

| 1   | 1   | 0  | 0 | 0 | 0 | 0 | 0  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0  | CØØØ    | RAM3         |

| 1   | 0   | 1  | 1 | 1 | 1 | 1 | 1  | 1             |   |   | 1 |   | _ |   | -  |         |              |

|     |     |    |   |   |   |   |    | <u>'</u>      | ' | 1 |   | 1 | 1 | 1 | 1  | BFFF    | RAM2         |

| 1   | 0   | 0  | 0 | 0 | 0 | 0 | 0  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 8000    |              |

| 0   | 1   | 1  | 1 | 1 | 1 | 1 | 11 | 1             | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 7FFF    |              |

| 0   | 1   | 0  | 0 | 0 | 0 | 0 | 0  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 4000    | MSX<br>BASIC |

| 0   | 0   | 1  | 1 | 1 | 1 | 1 | 1  | 1             | 1 | 1 | 1 | 1 | 1 | 1 | 1  | 3FFF    | ROM          |

| 0   | 0   | 0  | 0 | 0 | 0 | 0 | 0  | 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0000    |              |

Fig. 3-3-14 Memory allocation

As Fig. 3-3-14 shows, the MMC chips allot the two D-RAM chips to the memory.

Table ... Memory allocation

If we take into consideration address data A0  $\sim$  A13 only as in Fig. it becomes evident that when the CPU sends address data as output to the 14 address lines, addresses get simultaneously selected in MSX-BA-SIC-ROM, RAM2, and RAM3. Now, if two more bits (A15, A14) are added to the 14 address lines, then we get a total of 16 address lines; only one address can be selected in the 64K bytes (65536 addresses) are from 0000H to FFFFH.

In other words, the 2-bit address lines A15 and A14 serve to assign the MSX-BASIC-ROM chips (32K bytes), RAM2 (16K bytes), and RAM3 (16K bytes) correctly to the 64K byte memory area.

Figure 3-3-13 shows that those address lines A15 and A14 are decoded in the MMC chips after their entry from the CPU (Z-80A). This generates the following signals, the respective memory chips being assigned to the memory.

In the first instance above, RAM3 will be selected. In 2, RAM2 will be selected and in 3 the selection will be for MSX-BASIC-ROM.

# 4. THE SLOT CONCEPT AND THE MSX MEMORY CONTROLLER (MMC, YM5214)

Over here we shall offer a simple description of the Slots, a very important characteristic feature of the CX-5M microcomputer. At the same time, we shall have a look at the MMC (YM-5214) controlling the entire memory area in this system.

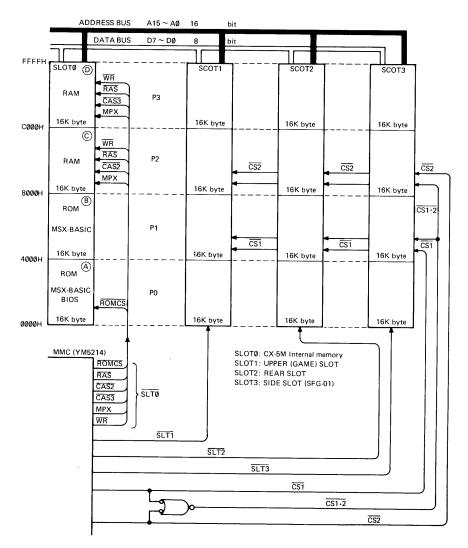

Fig. 4-1-1 CX-5M Slots Area Block Diagram

# 4-1 CX-5M memory area

The CPU (Z-80A) described so far uses a 64K byte memory area. In the CX-5M, this memory area is allotted to the area referred to as slot 0. It is used as ROM and D-RAM.

The following will give an idea about the 64K byte memory area.

Fig. 4-1-2 Memory Block Diagram: 64K Bytes in the Mainframe (CX-5M)

- 1. In the CX-5M, 16K bytes each are blocked together to form units to map the memory by

- 2. Each block is mapped as follows, using address bits A14 and A15.

| A15 | A14 | MEMORY EREA   | PAGE   |

|-----|-----|---------------|--------|

| 1   | 1   | CØØØH ~ FFFFH | 3 PAGE |

| 1   | Ø   | 8000H ~ BFFFH | 2 PAGE |

| Ø   | 1   | 4000H ~ 7FFFH | 1 PAGE |

| Ø   | Ø   | ØØØØH ~ 3FFFH | Ø PAGE |

Fig. 4-1-3 Mapping Table

- 3. Each 16K bytes block forms a page as shown in the figure.

- 4. As shown in Fig. 4-1-4 if the CPU accesses pages 0 and 1 (MSX-BASIC-ROM: 32K bytes), 2<sup>15</sup> or 32768 bytes of addresses may be selected from. These relate to 15 lines A0-A14 directly entering the ROM. These are arranged by ROMCS in memory area 0000H-7FFFH.

Fig. 4-1-4

5. As shown in Fig. 4-1-4 for pages 2 ~ 3, (D-RAM: 16K bytes x 2 blocks) direct selection of 2<sup>14</sup> = 16384 byte addresses is possible by address lines A0 ~ A13. Also, by using the CAS2 signal, a 16K byte D-RAM page 2 is mapped in the area 8000H-BFFFH while by using CAS3, the 16K byte D-RAM page 3 is mapped in C000H-FFFFH. Slot 0 (memory area in the CX-5M mainframe) and slots 1-3 are related as snown below.

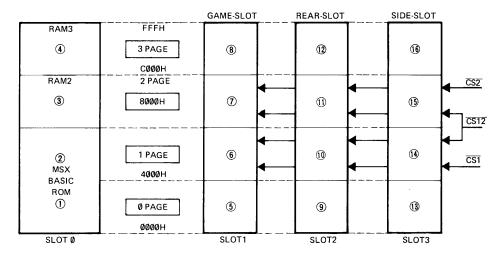

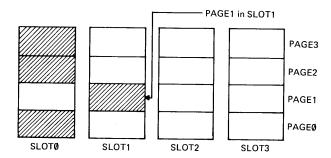

Fig. 4-1-5 Slots Map

The CX-5M can be provided with a 64K byte memory area each for slots 1-3 also (Fig. 4-1-5). Furthermore, the MSX specifications allow three slots to be added for each of the existing slots. Thus, there is provision for altogether 16 slots (1M bytes) in the memory area.

This manual covers only the configuration normally used (Fig. 4-1-5).

In the CX-5M, the individual slots are referred to as follows:

SLOT 1 = UPPER SLOT (GAME SLOT)

SLOT 2 = REAR SLOT

SLOT 3 = SIDE SLOT

All these are external slots.

# 4-2 MACHINE LANGUAGE PROGRAM EXTENSION

In the following, we shall assume that the machine language program in Fig, 4-2-1 is extended into page 1 in slot 1 (with the program cartridge inserted into the upper slot).

Normally, if the MSX-BASIC language is used, the entire 64K byte area from 0000H to FFFFH in slot 0 can be accessed for (read/write) operations, using the address data (A0-A15) from the CPU. If, however, the program ROM is extended to the page 1 in slot 1, then the process followed is an described below. As a result, all accesses to the page 1 block of slot 1 for read operation are switched to slot 1.

- 1. When power is on, all pages are set to be selected from slot 0.

- Starting from slot 1, a check is made to find out if programs are extended in pages 1 and 2 of the respective slots.

- 3. If a program is found to be extended in some area, a check is made to ascertain the program type and the data is written in the specific work area provided for the purpose in the mainframe (D-RAM).

- 4. The LSIs and other circuit components in the CX-5M are initialized.

- 5. Control is transferred to the program extension. Or, the MX-BASIC language mode is set up.

When the CPU has issued as output addresses 0000H-FFFFH, the following will take place.

Fig. 4-2-1 Memory Selection

In this way, a memory area with a total capacity of 64K bytes is built up.

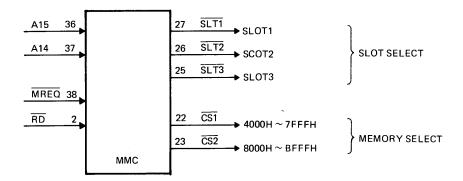

Normally, programs are extended in pages 1 and 2 of slots 1-3. The MMC chips issue the following signals to select (chip select) memory areas:

1. CS1

4000H-7FFFH

2. CS2

8000H-BFFFH

3. CS1,2

4000H-BFFFH

#### 4-3 Slot select signal

The following are the essential considerations underlying slot selection. As described so far, the slot select signals (SLOT 1, SLOT 2, and SLOT 3) determine the slot from which one of the pages (16K bytes each) is to be selected.

For example, if we consider page 0 alone as in Fig. 4-3-1, we have

Fig. 4-3-1 0 Page Block Map

If page 0 is selected from slot 1 (Fig. 4-3-1), and the CPU issues an address from 0000H to 3FFFH, then SLOT 1 signal along goes low while the other signals all go high.

This is what occurs in the other pages also.

Next, let us see how the slot select signal is generated.

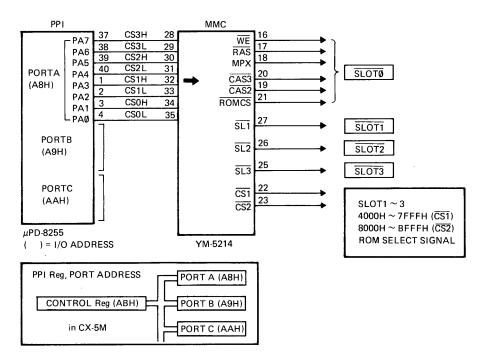

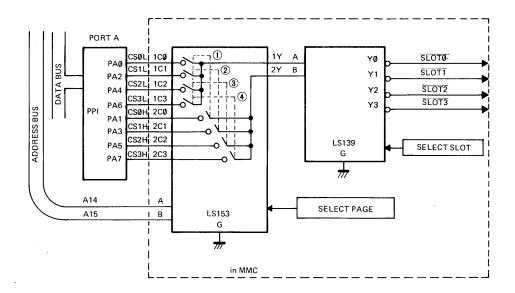

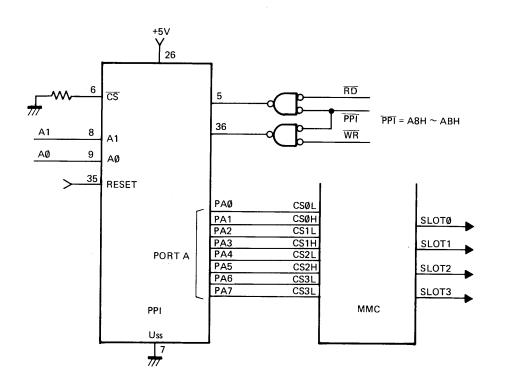

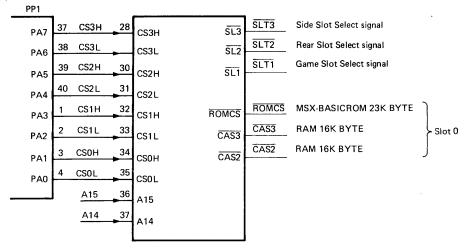

Fig. 4-3-2 Slot Signals Generated by the PPI and MMC

As Fig. 4-3-2 shows, the PPI and MMC chips generate the slot select signals.

The 8-bit output from port A of the PPI enter the MMC as they are. The respective bits of port A are as described  $\dots$

below:

PA0 and PA1: Determine the slot from which to select the page 0 area PA2 and PA3: Determine the slot from which to select the page 1 area

PA4 and PA5: Same as above except that page 2 or 3 is

PA6 and PA7: Substituted for page 0 or 1.

A slot is selected as follows according to the state of the two bits of PPI port A:

|       | PA0 | PA2 | PA4 | PA6 | PA1 | PA3 | PA5 | PA7 |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| SLOT0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| SLOT1 | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 0   |

| SLOT2 | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1   |

| SLOT3 | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

If all the pages are selected from slot 0, port A will be as follows:

| PA0 | PA1 | PA2 | PA3 | PA4 | PA5 | PA6 | PA7 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

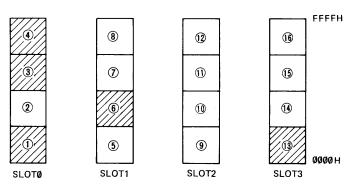

Fig. 4-3-3

If (1), (6), (3), (4) must be selected in Fig. 4-3-3:

| PA0 | PA1 | PA2 | PA3 | PA4 | PA5 | PA6 | PA7 |     |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | Ø4H |

If (13), (6), (3), (4) must be selected in Fig. 4-3-3:

| PA0 | PA1 | PA2 | PA3 | PA4 | PA5 | PA6 | PA7 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0   |

In this way, slot data to be selected for the respective pages are set in port A I/O Address A8H of the PPI and entered in the MMC. As a result, the respective slot select signals are issued by the decode circuit shown in Fig. 4-3-4.

LS153

|   | INPUT |     | OUTPUT |     |  |

|---|-------|-----|--------|-----|--|

| G | SEL   | ECT |        |     |  |

|   | В     | Α   | 1Y     | 2Y  |  |

| Н | X     | ×   | L      | L   |  |

| L | L     | L   | 1CØ    | 2CØ |  |

| L | L     | Н   | 1C1    | 2C1 |  |

| L | Н     | L   | 1C2    | 2C2 |  |

| L | Н     | н   | 1C3    | 2C3 |  |

LS139

| ı        | NPUT | •   |        | OUTPUT |    |    |  |

|----------|------|-----|--------|--------|----|----|--|

| G        | SEL  | ECT | OUTFOI |        |    |    |  |

| <u> </u> | В    | Α   | ΥØ     | Y1     | Y2 | Y3 |  |

| н        | Х    | х   | Н      | Н      | Н  | Н  |  |

| L        | L    | L   | L      | Н      | Н  | Н  |  |

| L        | L    | Н   | Н      | L      | Н  | Н  |  |

| L        | Н    | L   | Н      | Н      | L  | Н  |  |

| L        | Н    | Ξ   | Η      | Н      | Н  | L  |  |

SELECT PAGE

| A15 | A14 |               | PAGE          | PPI PORTA |

|-----|-----|---------------|---------------|-----------|

| L   | L   | <b>Ø</b> PAGE | 0000H ~ 3FFFH | CSØL, H   |

| L   | Н   | 1PAGE         | 4000H ∼ 7FFFH | CS1L, H   |

| Н   | L   | 2PAGE         | 8000H ~ BFFFH | CS2L, H   |

| Н   | Н   | 3PAGE         | C000H ~ FFFFH | CS3L, H   |

SELECT SLOT

| SLOT | CSL, | CSH |

|------|------|-----|

| Ø    | Ø    | Ø   |

| 1    | 1    | Ø   |

| 2    | Ø    | 1   |

| 3    | 1    | 1   |

| PPI Reg ADR  | A7 ~ A2 | A1 | AØ | RD = "L", WR = "H" | RD = "H", WR = "L" |

|--------------|---------|----|----|--------------------|--------------------|

| A8H (PORT A) | 10101X  | 0  | 0  | IN                 | OUT                |

| A9H (PORT B) | 10101X  | 0  | 1  | (IN)               | OUT                |

| AAH (PORT C) | 10101X  | 1  | 0  | IN                 | OUT                |

| COMMAND Reg  | 10101X  | 1  | 1  |                    | COMMAND Reg WRITE  |

Fig. 4-3-4, 4-3-5 Slot-Select Signal (MSX-Specification)

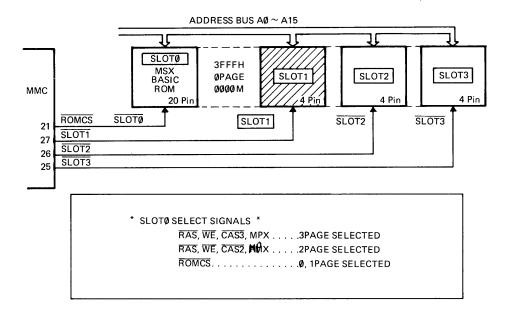

The MMC chips used in CX-5M perform the following control operations:

1. Memory select for slot 0

Fig. 4-3-7

- 2. Slot select signal for slots 1-3

- 3. Memory select for slots 1-3

Fig. 4-3-8

4. Address select for the I/O port.

The MMC chips used in CX-5M perform the following control operations:

1. Memory select for slot 0

Fig. 4-3-7

- 2. Slot select signal for slots 1-3

- 3. Memory select for slots 1-3

Fig. 4-3-8

4. Address select for the I/O port.

Fig. 4-3-9

**- 56 -**

# 5. I/O PORT BLOCK

The CPU and memory blocks discussed so far meet the minimum requirement for microcomputer system operations. However, the operator cannot enter from outside data or command for CPU control, nor receive or display different types of control data items or results of operations performed by the CPU.

This raises the need for devices which receive data from outside and output results to outside.

Fig. 5-1-1 I/O Devices Block Diagram

The special areas used for connection with such devices are referred to as the input/output port area or I/O interface.

Fig. 5-1-2 Block Diagram of I/O Devices Ports

The I/O port allows read/write (input/output) operation just as the memory area in RAM chips do.

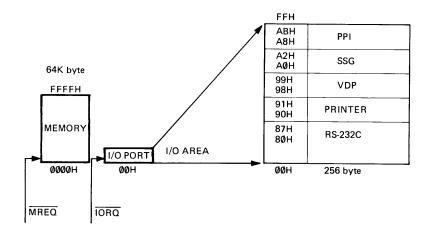

The CPU Z-80A used in the CX-5M has a main memory area (64K bytes) and an I/O area (256 bytes).

Fig. 5-1-3 CX-5M I/O Port Memory Map

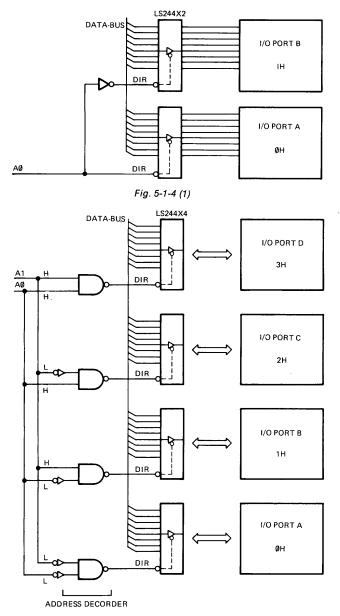

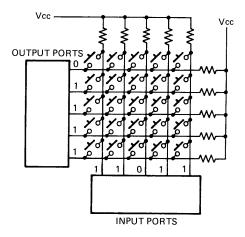

Data from the CPU is output to the devices on ports A and B through one address line (A0) (Fig. 5-1-4 (1)).

In the case of Fig. 5-1-4 (2), data is output to the four ports designated by two address lines (A0, A1).

Fig. 5-1-4 (2)

In this way, the Z-80A CPU is connected through eight addresses lines to 256 I/O port addresses.

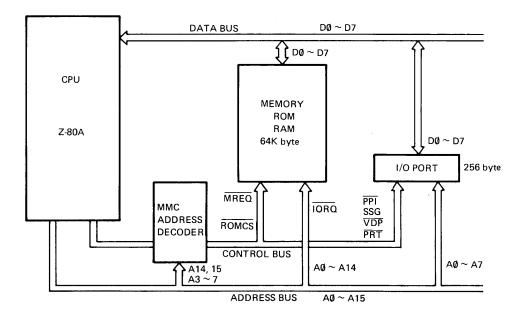

The CX-5M I/O port block diagram appears below.

Fig. 5-1-5 I/O Port Block Diagram

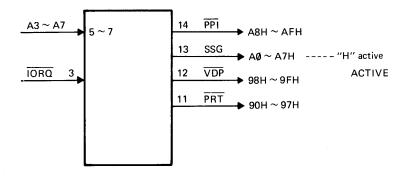

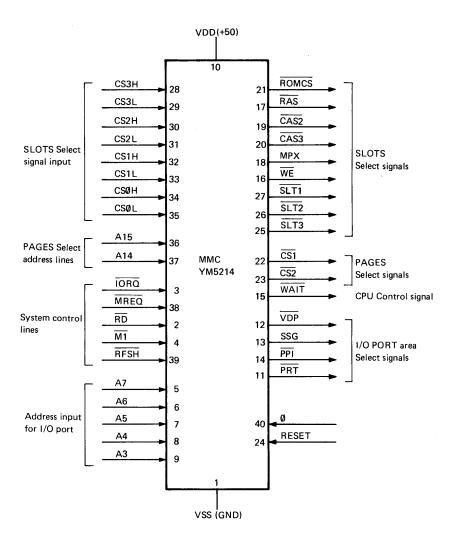

# 5-1 I/O PORT CONTROL BY THE MMC CHIPS

Except the LPT (printer) port, all the I/O ports are implemented on the 40-pin LSIs (Fig. 5-1-6 (1)). The MMC chips control all these I/O ports.

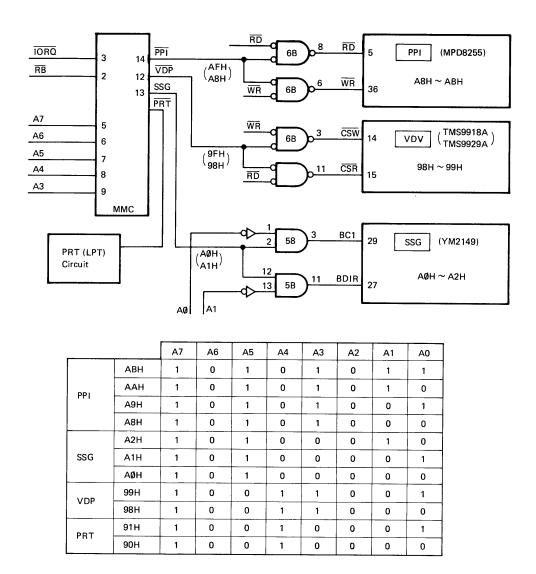

Fig. 5-1-6 (1) and (2) Block Diagram of I/O Ports and the MMC

IORQ entering the MMC chips is a system control signal indicating that the Z-80A CPU has selected the I/O port area.

Address lines A3  $\sim$  A7 are decoded inside the MMC chips on the basis of which I/O ports are assigned to the respective areas 00H-FFH.

Fig. 5-1-7

# 5-2 I/O Ports and Their Peripherals

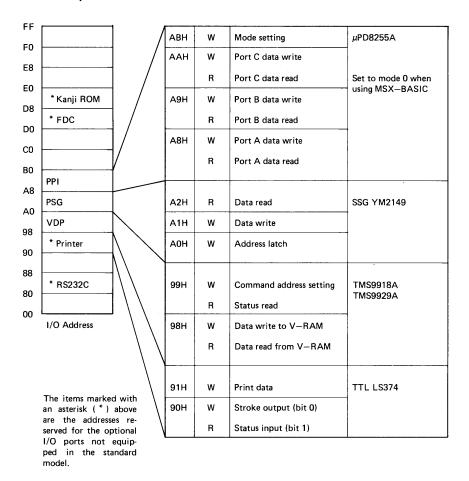

#### CX-5M I/O port address map

According to the MSX specifications, the 256 byte Z-80A I/O port area from 00H to FFH is reserved for the standard MSX system devices as follows:

Fig. 5-2-1

Addresses 80H to FFH are set as above as I/O port addresses. Addresses 00H to 7F can be used freely. Basically, however, for I/O devices not specified above, I/O port addresses must be set in the memory space by applying the memory mapped I/O method. This is because the system will not operate if the I/O port address space (which is not subject to slot selection) is used simultaneously with some other device.

# 5-3 I/O Peripheral Circuit

The following devices are interfaced to the Z-80A peripheral circuit (microcomputer system) and the I/O peripheral circuit using the I/O port addresses described in the earlier section.

#### 5-3-1 I/O Devices Controlled by PPI (μPD8255)

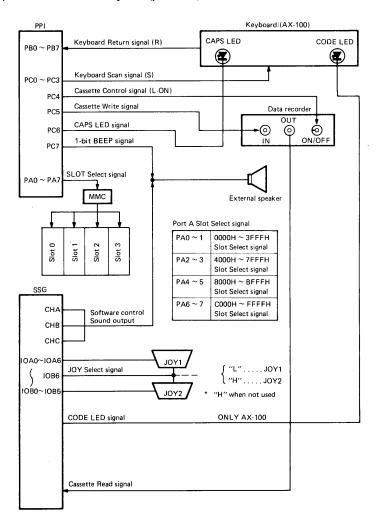

Fig. 5-3-1 External I/O Configuration Based on PPI and SSG I/O Ports

# 5-3-2 SSG (YM-2149) Controlled I/O Devices

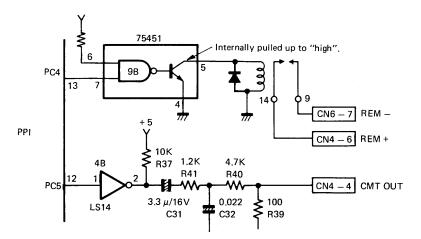

Pins to be controlled by PPI ( $\mu$ PD8255)

| Kauhaand aantual     | Port B | PB0 ~ PB7 | Scanning-Data-In X0 ~ X7         |

|----------------------|--------|-----------|----------------------------------|

| Keyboard control     | Port C | PC0 ~ PC3 | Scanning-Data-Out Y0 ~ Y9        |

| CMT control (on/off) | Port C | PC4       | Recorder-Motor-On/Off-Signal-Out |

| CMT data output      | Port C | PC5       | Recorder-Data-Out                |

| CAP LED control      | Port C | PC6       | CAP-Lock-LED-Control-Signal-Out  |

| Alarm sound output   | Port C | PC7       | Beep-Sound-Out                   |

| Slot select output   | Port A | PA0 ~ PA7 | Slot-Select-Signal-Out           |

#### Pins to be controlled by SSG (YM-2149)

|                                   | СНА |             | 8 octaves, tri-chord sound plus noise<br>Envelopes are controlled collectively<br>(not individually). |  |

|-----------------------------------|-----|-------------|-------------------------------------------------------------------------------------------------------|--|

| Software controlled sound output  | СНВ |             |                                                                                                       |  |

|                                   | СНС |             |                                                                                                       |  |

| General I/O port control          | IOA | 10A0 ~ 10A5 | Scanning-Data-In                                                                                      |  |

| General 1/O port control          | IOB | IOB0 ~ IOB5 | Scanning-& Strobe-Signal-Out                                                                          |  |

| General I/O port selection        | IOB | IOB6        | General-I/O-Port 1, 2-Select-Signal-Out                                                               |  |

| Kana-LED Control (non used)       | IOB | IOB7        | Kana-Lock-LED-Control-Signal-Out                                                                      |  |

| Keyboard-arrangement-select input | IOA | IOA6        | Japanese/JIS-Keyboard-Arrangement-<br>Select                                                          |  |

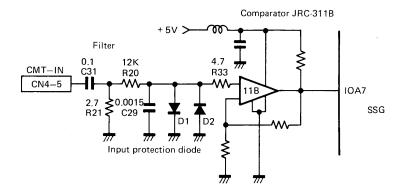

| CMT data input                    | IOA | IOA7        | Recorder-Data-In                                                                                      |  |

Fig. 5-3-2 (A)(B)

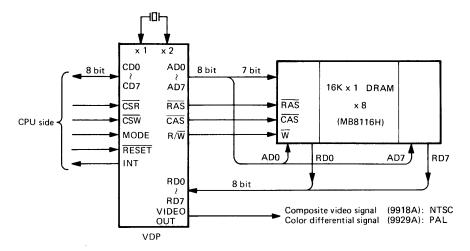

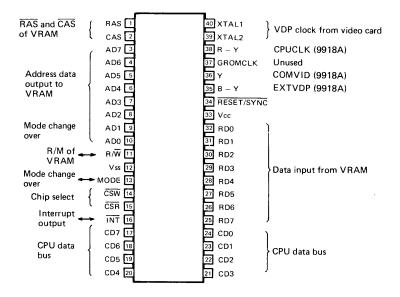

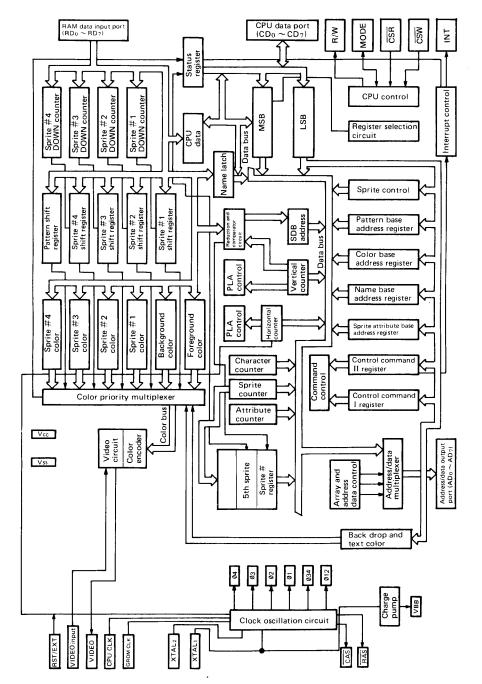

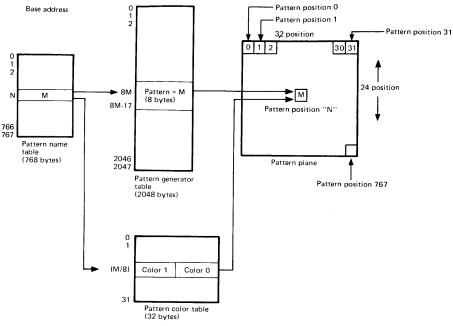

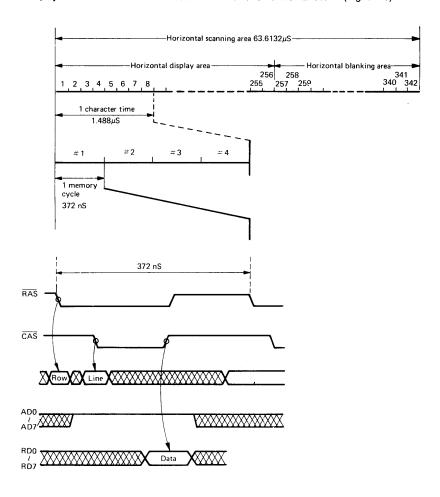

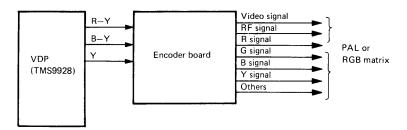

# 5-3-3 VDP (TMS9929A, TMS9918A) Video Display Processor

Performs all control operations for the CRT. For details, refer to the material provided separately.

#### 5-3-4 Printer control

# Eight-bit parallel

Hand-shake based on Busy and Strobe signals.

#### Level TTL output:

Conforms to JIS. Anphenol 14-pin connector.

#### 5-4 Outline of PPI (mPD8255A) operation

#### Basic I/O port control operation

Fig. 5-4-1 Internal Block Diagram in PPI Control Mode 0

Shown above is the internal mode diagram (mode 0) of the PPI. In the MSX system, the PPI (mPD8255A) is set with I/O port addresses A8H-ABH. The CPU selects and controls the RD, WR, CS, A1, and A0 lines, and thereby controls the command registers and the R/W control block Fig. 5-4-1. In this way, it controls the operations of, respectively, ports PA, PB, and PC.

In the above figure, all the 24 pins (PA-PC) appears as I/O port terminals. Depending on the way you use port PC, there are three modes:

$\label{eq:MODE 0: MODE 0: MO$

MODE 1: 8-bit handshake mode (independent of each other ports PA and PB)

MODE 2: Bidirectional handshake mode ( " )

#### 5-4-1 Mode setting from command registers

When MSX-BASIC is activated, the PPI is set in Mode 0. All the discussions from now on will center on Mode  $\alpha$

As already shown, the MSX system uses the four I/O port addresses A8H-ABH (4 bytes) and selects the following internal addresses Fig. 5-4-2:

| A1 | A0 | I/O Address | R – NAME    | R/W                |                                 |                  |                  |  |

|----|----|-------------|-------------|--------------------|---------------------------------|------------------|------------------|--|

| 0  | 0  | А8Н         | PA Register | R/W                | Internal I/O data latch address |                  |                  |  |

| 0  | 1  | А9Н         | PB Register | R/W                | ,,                              | ,,               | ,,               |  |

| 1  | 0  | ААН         | PC Register | R/W                | "                               | ,,               | "                |  |

|    |    | 4.011       | Control     | Control W register | D7 = 1                          | Command register |                  |  |

| '  |    | ABH regi    | register    |                    | D7 = 0                          | For PC regi      | ster bit control |  |

Fig. 5-4-2

These I/O ports are selected and controlled by the five signal lines fed to the command registers and the R/W control block.

RD: Reads the contents of the selected register when low, and sends them to the CPU

WR: Writes from the CPU into the selected register when low.

CS: Chip-selects the PPI (mPD8255A) when low.

A1  $\sim$  A0: Directly connected to the address bus. This signal selects a register inside the

PPI.

The following conditions are required when the PA-PC I/O states must be controlled by the command registers.

RD = "H" WR = "L" CS = "L"

The MSB (D7) of the data to be written is always '1'.

\*When D7 = 0, the PC port is controlled bitwise.

The above setting latches in the command registers shown in the figure the data determining whether input or output will be performed at the respective ports (PA-PC). Till the data is re-written, ports PA-PC will be used for input or output as decided above.

When MSX-BASIC is activated, the following I/O status will prevail:

PA port: For output to the MMC

PB port: For input of keyboard data, RETURN, and DATA

PC port: For output of keyboard data, cassette data, cassette control, and CAPS-LED

The format of the data written in the command registers is as shown below (Mode 0: write only):

| D7 | D7 = 1 for addressing a command register by D6 $\sim$ D0. D7 = 0 for the Bit control of the PC port. |                |                 |  |  |  |

|----|------------------------------------------------------------------------------------------------------|----------------|-----------------|--|--|--|

| D6 | Sets the PA group mode<br>D6 and D5 are both set to zero in the MSX system.                          |                |                 |  |  |  |

| D5 | D6 = 0, D5 = 0 : MODE 0 D6 = 0, D5 = 1 : MODE 1 D6 = 1, D5 = 1, 0 : MODE 1                           |                |                 |  |  |  |

| D4 | Sets the I/O direction of the PA port.                                                               | D4 = 1 : INPUT | D4 = 0 : OUTPUT |  |  |  |

| D3 | Sets the I/O direction of the PC port bits $4 \sim 7$ .                                              | D3 = 1 : INPUT | D4 = 0: OUTPUT  |  |  |  |

| D2 | Sets the PB group mode.                                                                              | D2 = 1 : MODE1 | D2 = 0 : MODE0  |  |  |  |

| D1 | Sets the I/O direction of the PB port.                                                               | D1 = 1 : INPUT | D1 = 0: OUTPUT  |  |  |  |

| D0 | Sets the I/O direction of the PC port bits $0 \sim 3$ .                                              | D0 = 1 : INPUT | D1 = 0 : OUTPUT |  |  |  |

Fig. 5-4-3

D7-D0 will be set as shown below when MSX-BASIC is activated.

| D7 | 1 | Command Register selection                              |  |  |  |

|----|---|---------------------------------------------------------|--|--|--|

| D6 | 0 | Cota the DA port to made 0                              |  |  |  |

| D5 | 0 | Sets the PA port to mode 0.                             |  |  |  |

| D4 | 0 | Sets the PA port to the output port.                    |  |  |  |

| D3 | 0 | Sets the 4 to 7 bits of the PC port to the output port. |  |  |  |

| D2 | 0 | Sets the PB port to mode 0.                             |  |  |  |

| D1 | 1 | Sets the PB port to the input port.                     |  |  |  |

| D0 | 0 | Sets bits 0 to 3 of the PC port to the output port.     |  |  |  |

This setting is performed by writing "10000010" (= "82" in hexadecimal) in the ABH address (I/O address).

Set D7, D6, D5, and D2 respectively to 1, 0, 0, and 0. Set D4, D3, D1, and D0 command registers.

Set D7-D0 by writing 10 00 00 10 = 82H in I/O address ABH.

Fig. 5-4-4

Input/output for the ports PA-PC is set as above. In the MSX system, ports PA and PC are set to output and port PB to input.

When the data in port PA is given out as output, the process that follows is as shown below:

A1 = A0 = "0" .... PA register select ..... A8H The output data is written in the selected PA register.

The above will start data output at port PA.

#### Outline of the PPI MSX system operation

As indicated in Table 3 and Fig. 16, ports PA-PC of PPI are set in the MSX system. The circuits (interface circuits) connected to the respective ports are as shown below:

#### (1) Slot select function with PA0 $\sim$ PA7

Fig. 5-4-5

If an 8-bit CPU is used, only a 64K byte area can be addressed normally. However, in case that the system can be upgraded in the future, the MSX system allows a memory area extension of 64K bytes (besides the main 64K byte area) referred to as slots.

This 64K-byte area is divided into four blocks, 16K bytes each, so that memory selection can be made within slots.

| FFFFH | A15 A14          |     |       |       |       |  |

|-------|------------------|-----|-------|-------|-------|--|

| С000Н | 16K BYTE<br>RAM  | 1 1 | D     | н     | L     |  |

| 8000H | 16K BYTE<br>RAM  | 1 0 | С     | G     | к     |  |

| 6000H | 32K BYTE         | 0 1 | В     | F     | J     |  |

| 4000H | MSX-BASIC<br>ROM | 0 0 | А     | E     | I     |  |

| 0000H | SLOT0            |     | SLOT1 | SLOT2 | SLOT3 |  |

Slots 0  $\sim$  3 are selected by means of the respective slot select signals in Fig. 5-4-5. The 16K byte blocks are selected basically by A14 and A15.

Fig. 5-4-6

# Output data from port PA of the PPI generates the following select signals.

| PA Port |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS3     | Н | Circular arificing the sheet sheet along the control of the contro |

| CSS     | L | Signal specifying the slot that selects the area C000H $\sim$ FFFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CS2     | Н | Circular and friend the clot that release the area 9000H a DEFFH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CSZ     | L | Signal specifying the slot that selects the area 8000H $\sim$ BFFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CS1     | н | Signal specifying the slot that selects the area 4000H $\sim$ 7FFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

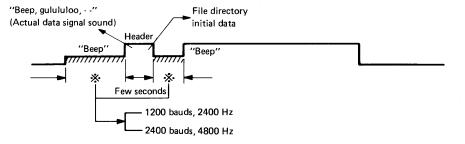

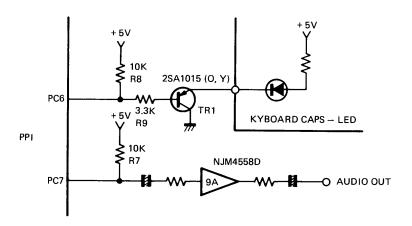

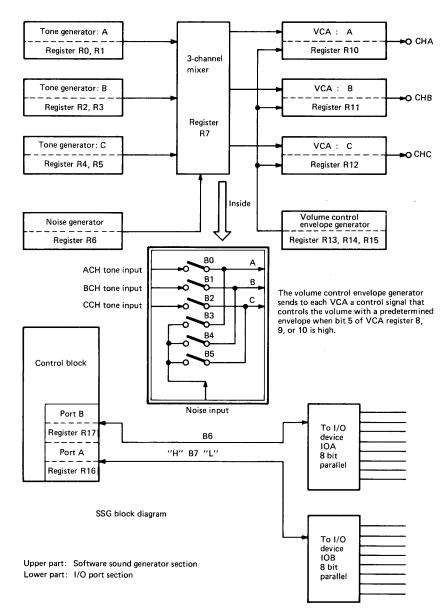

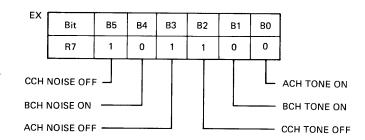

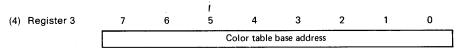

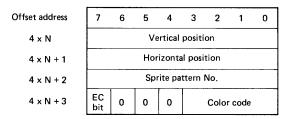

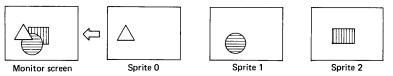

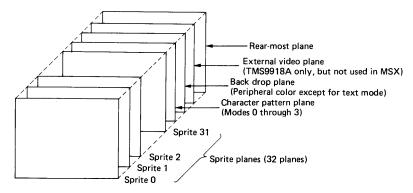

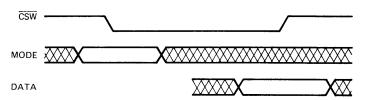

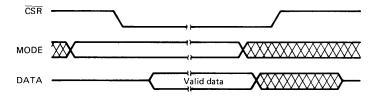

| CST     | L | Signal specifying the slot that selects the area 4000H ~ 7FFFH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |